PLC文化圏では、電子回路文化圏は別次元のものと思われているふしがあるようです

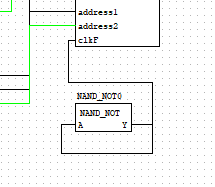

とりあえず 【NAND回路】をつくってみる-(IC屋さんの文化的に万能らしい)

*注意:物理接点リレーでの再現はかなり辛いですがやってる方もいるようです。

ということなので NAND2TETRIS を勝手に参考にして

OpenPLCでどこまで再現できるかやってみよう!!!!!!!

パチ パチ パチっ(拍手)

なぜわざわざNAND?

素子が安いかららしいです (OPENPLC上のみでやる分には意味はないです)

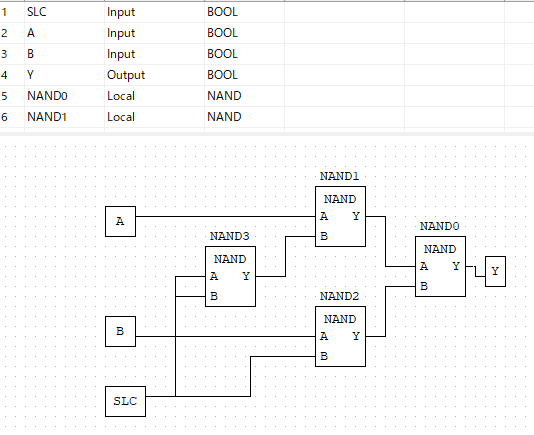

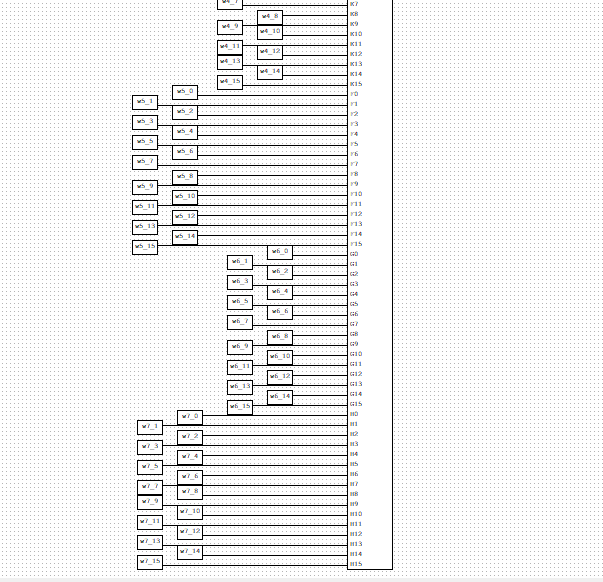

最小単位の構成の構築

FB化するーこれがすべてのもとになる予定

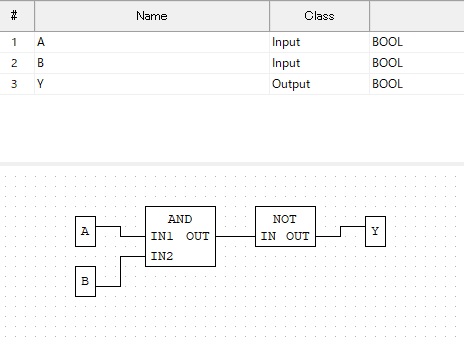

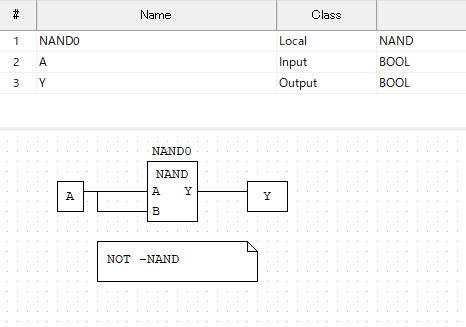

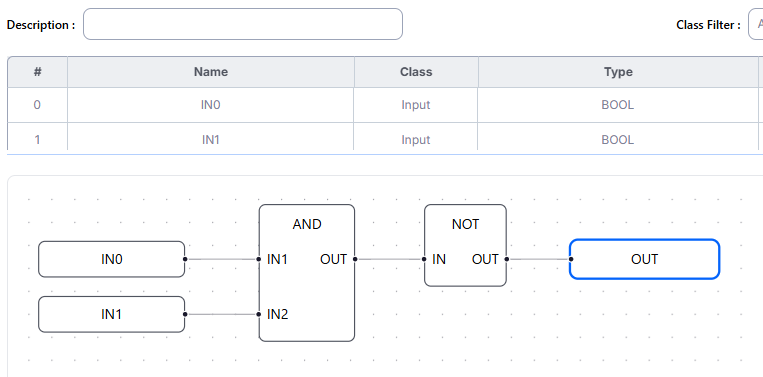

NANDでNOT

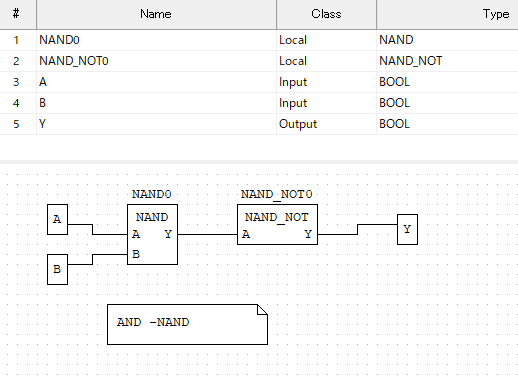

NANDでAND

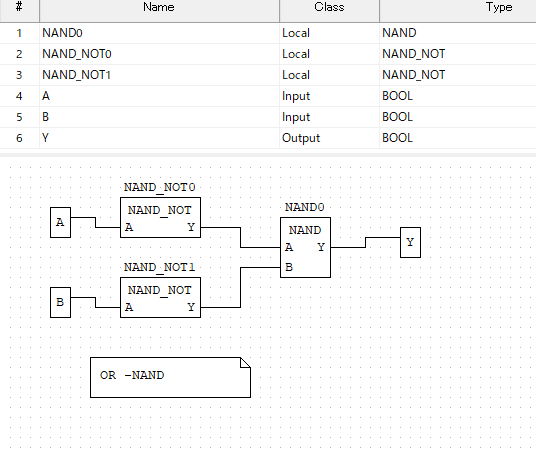

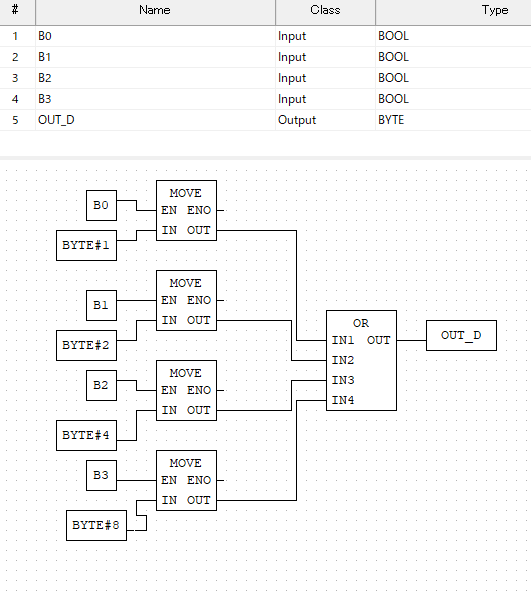

NANDでOR

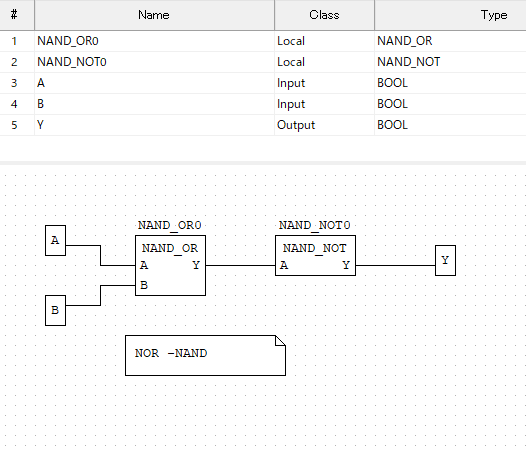

NANDでNOR

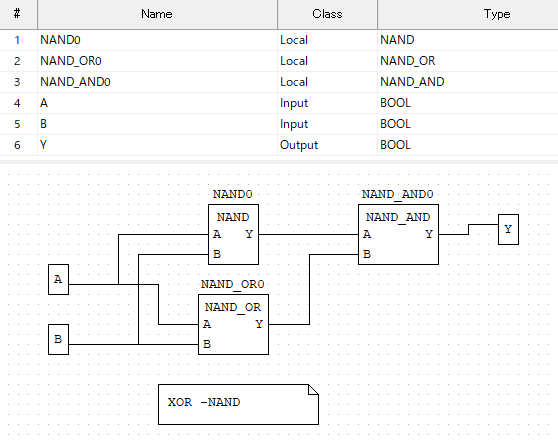

NANDでXOR

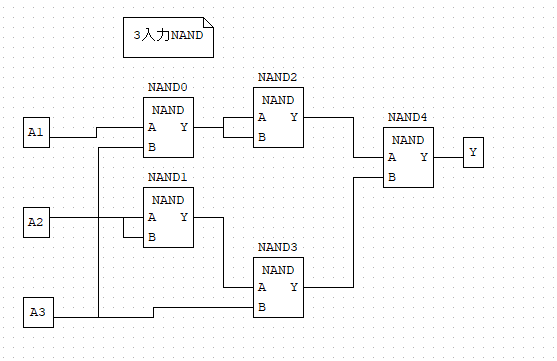

3入力NAND回路

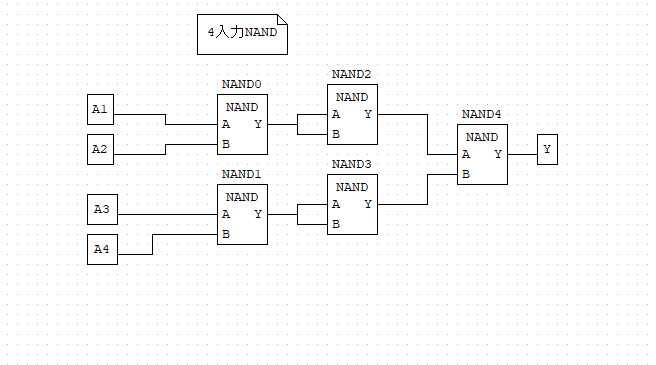

4入力NAND回路

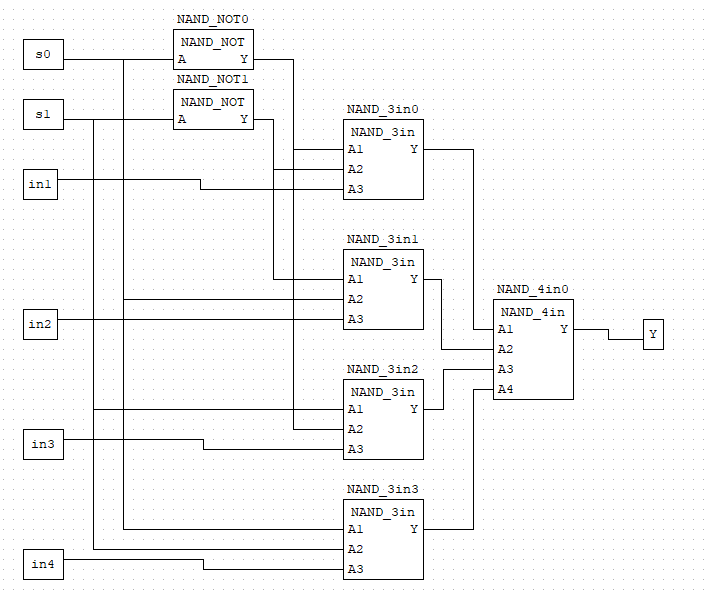

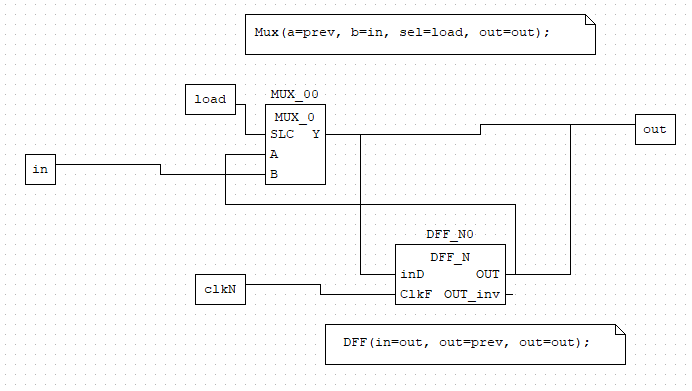

MUX 選択回路

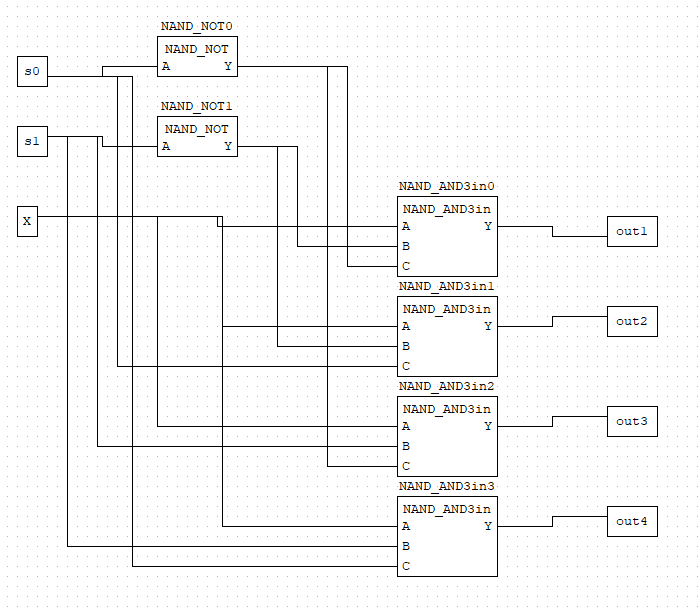

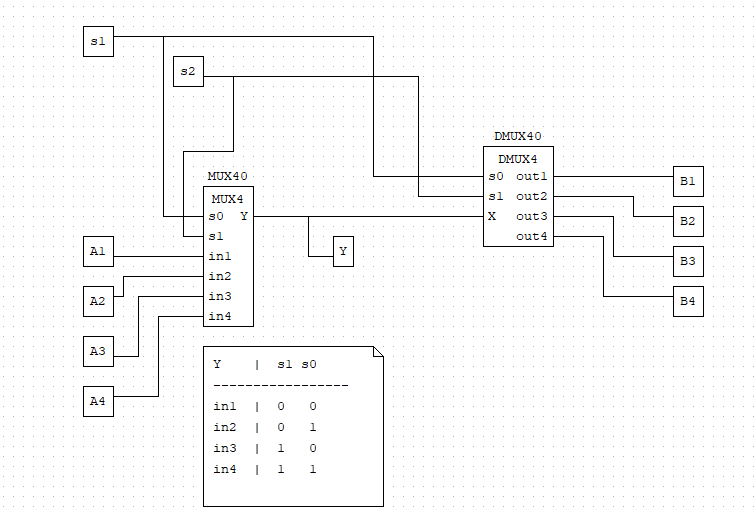

MUX4 – DMUX4 選択回路

MUX4 4つのなかから選択します

DMUX4 4つのどれかへ出力します

接続点がないから見えにくいんです

FB化 MUX4 TO DMUX4

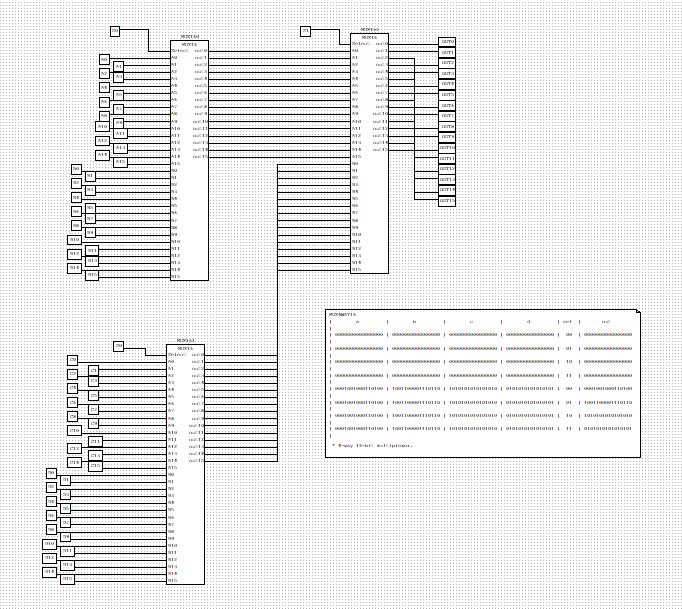

MUX4WAY16 【IEC61131-3がHDL対応にならないかしら】

本家GiT-HDLから脳内変換なので合ってるか不明です。(クリックしても拡大しません)

MUX16 を3つ使用します

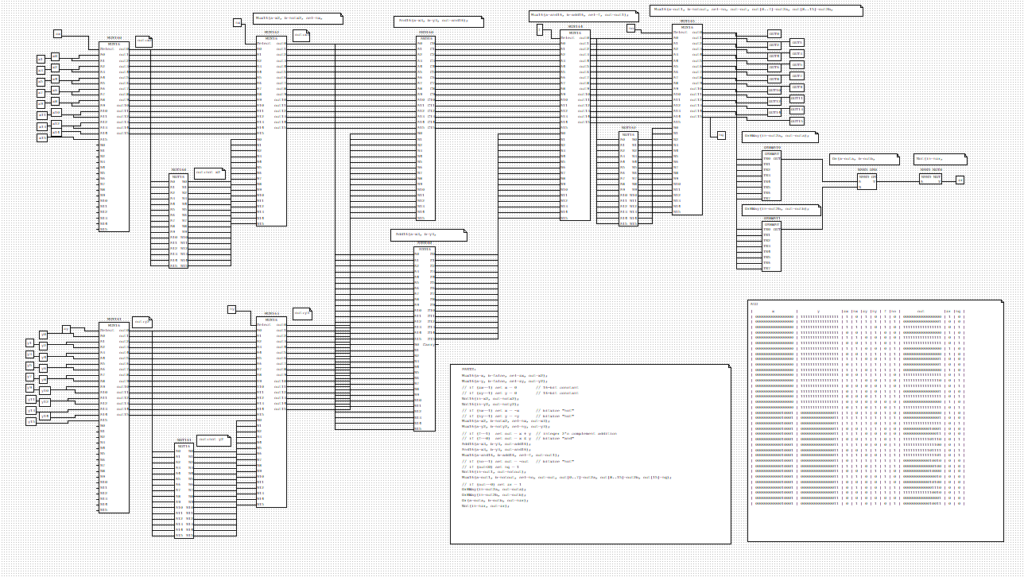

MUX8WAY16【ハード結線する場合は狂気の沙汰です】

MUX4WAY16を2つ、MUX16を1つ使います

(クリックしても拡大しません)

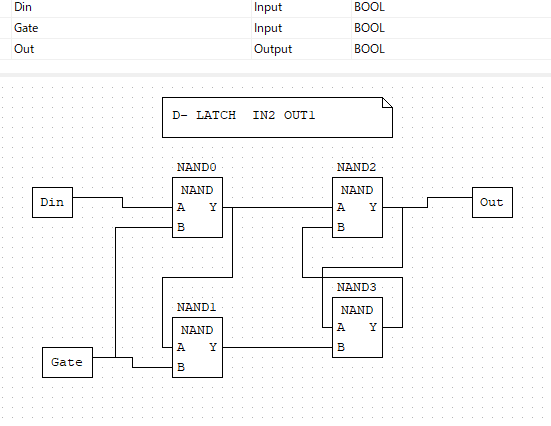

Dの一族:D-LATCH,D-FlipFlop

D-latch

D-FlipFlop

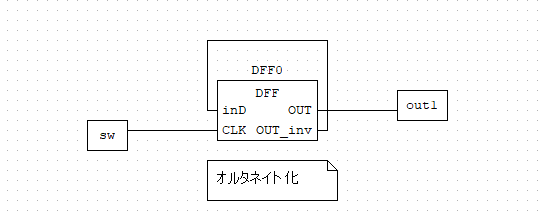

オルタネイトスイッチ 1個のスイッチでオン/オフする

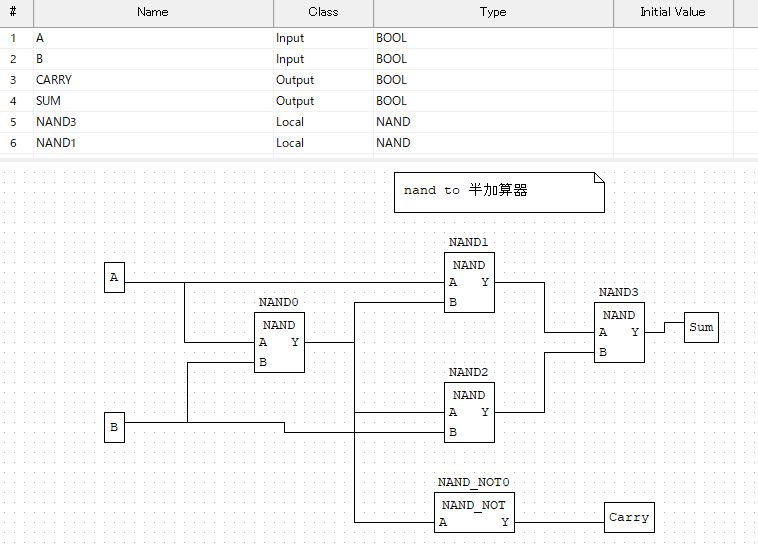

NANDによる半加算器 ー NANDを4つ使うんです

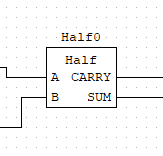

FB化する

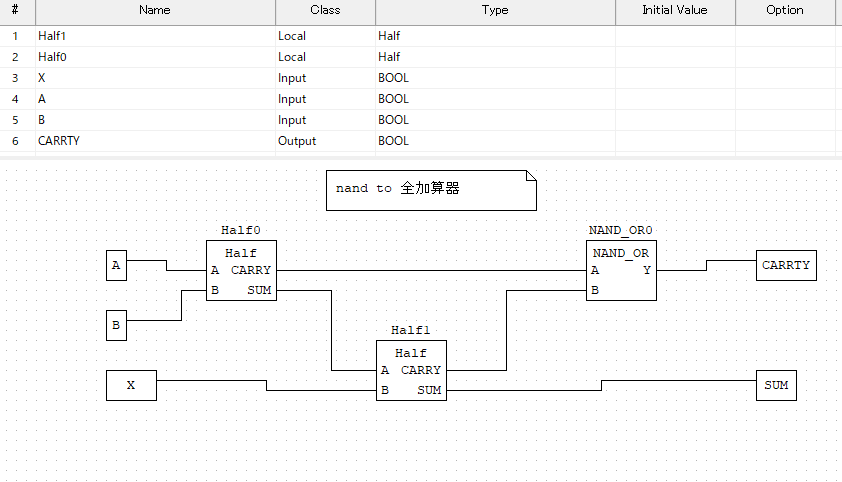

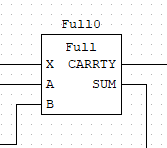

NANDによる全加算器 ー 半分が2つで1人前だそうです

FB化する

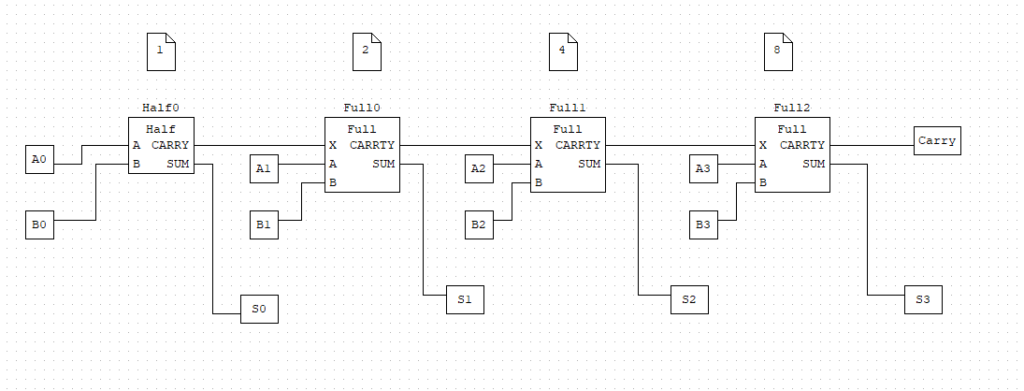

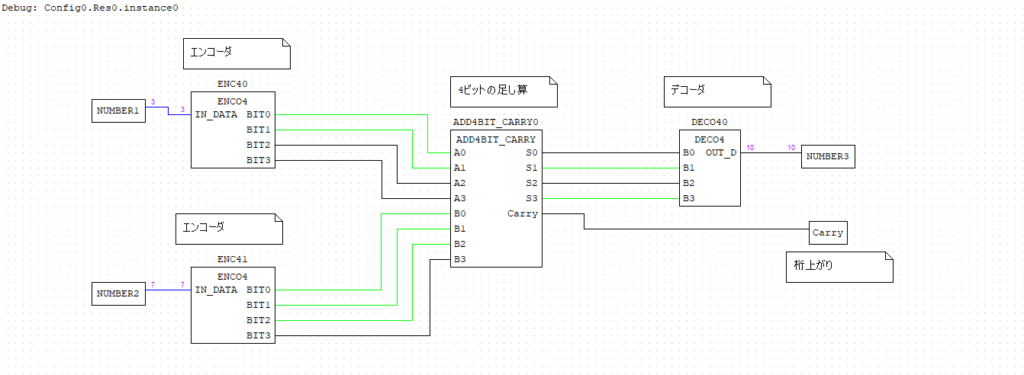

4桁の加算器 桁上がり付き

4桁の加算器のFB化

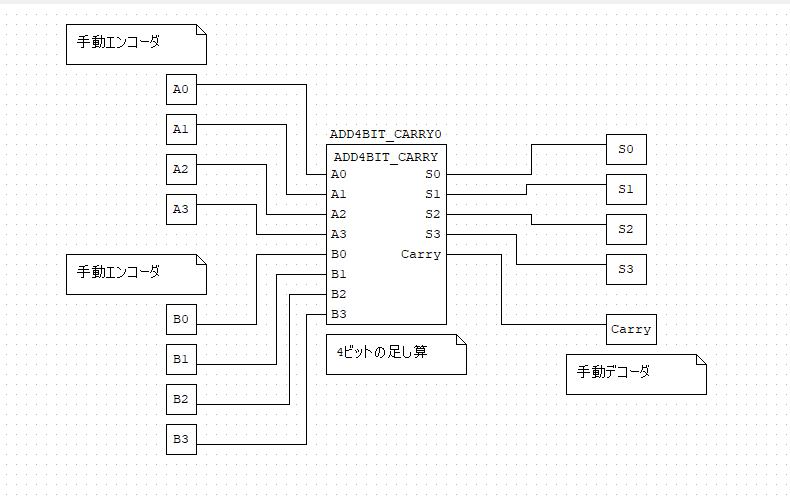

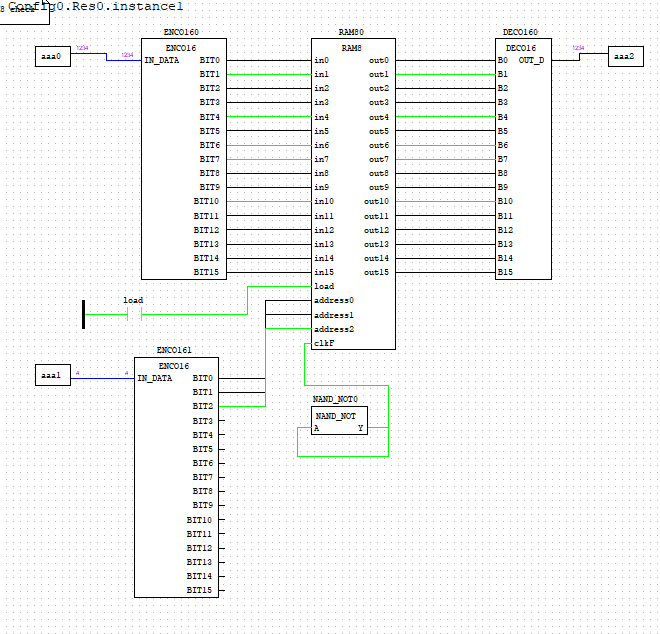

ついでにエンコーダとデコーダをつくってみる

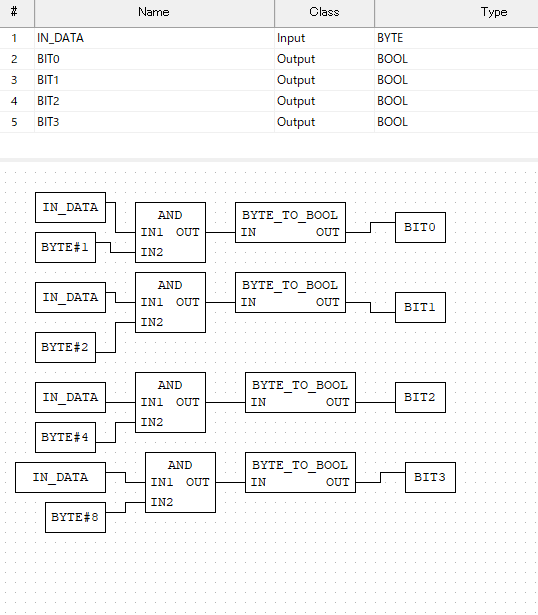

エンコーダ :10進数をビット列化にする

各ビットを確認してフラグを立てる

デコーダ :ビット列を10進数に変換する

ビットのフラグ確認で合成する

実装

3+7=10を計算出来ました。

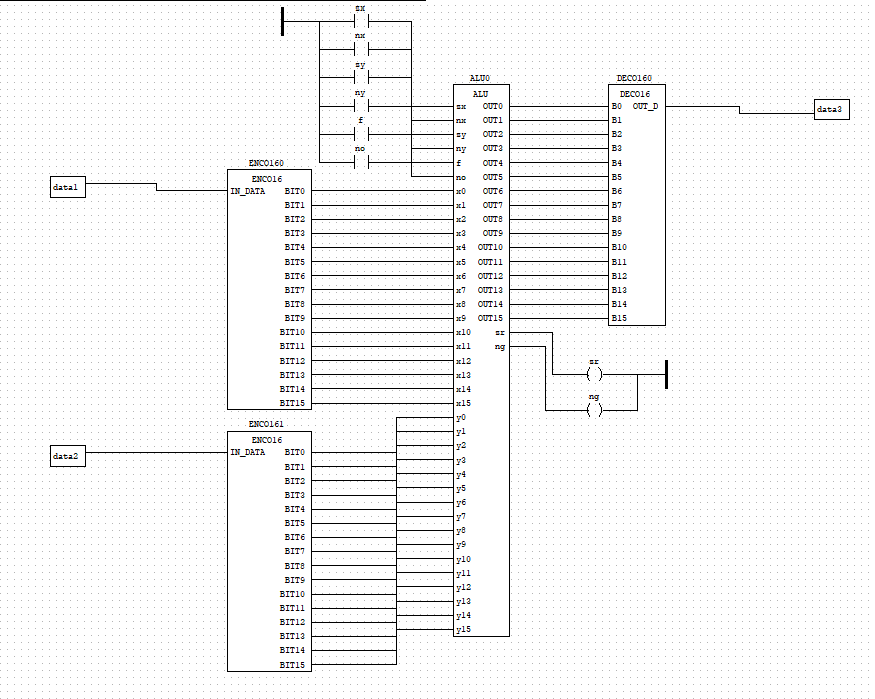

ALU (16ビット)

HDLもなんとなく読めるようになる

FB化で動作チェックする

bit -1ビットレジスタ

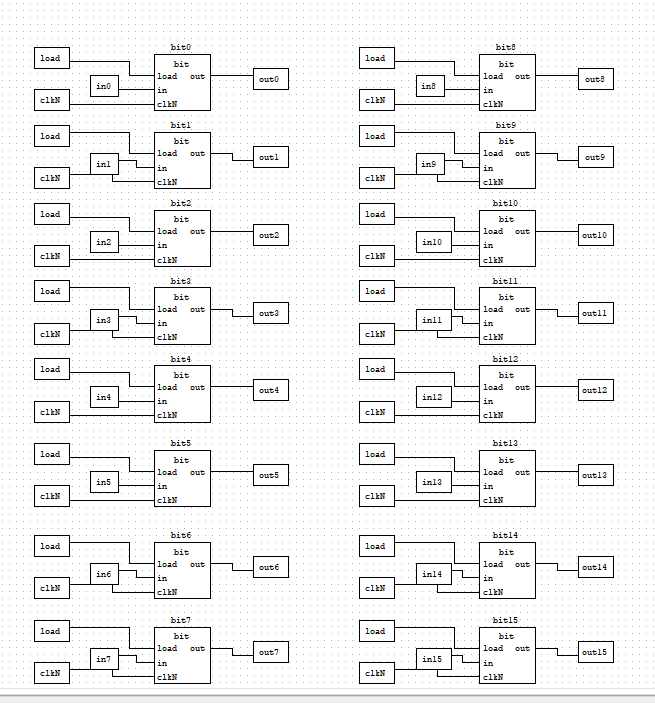

register -16bit レジスタ

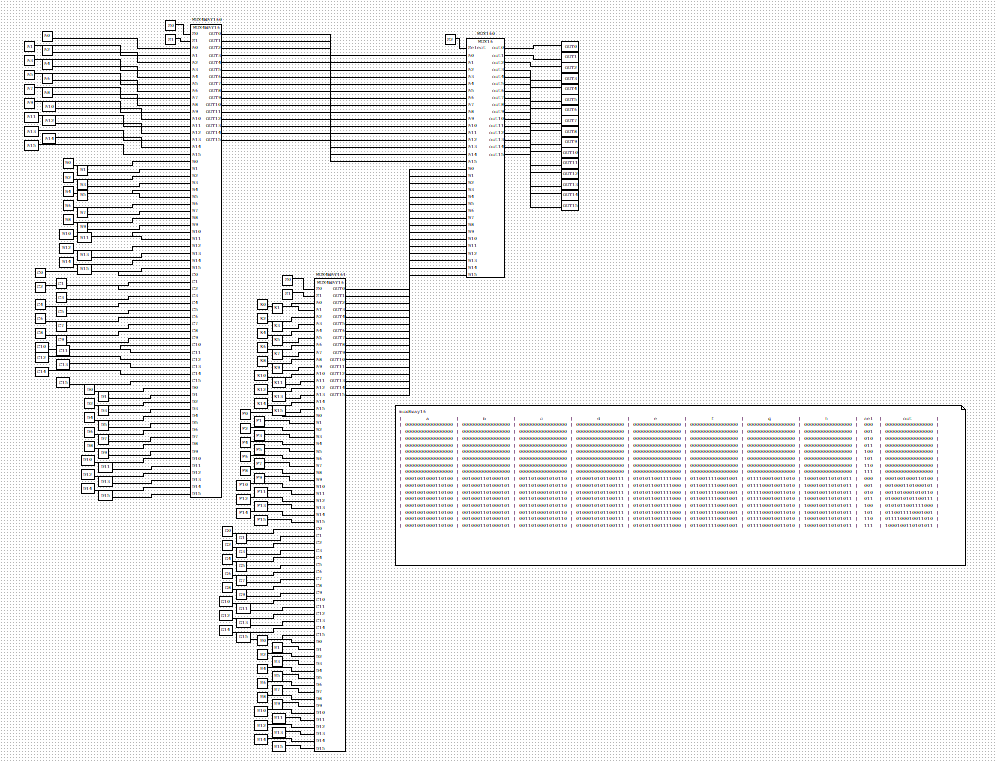

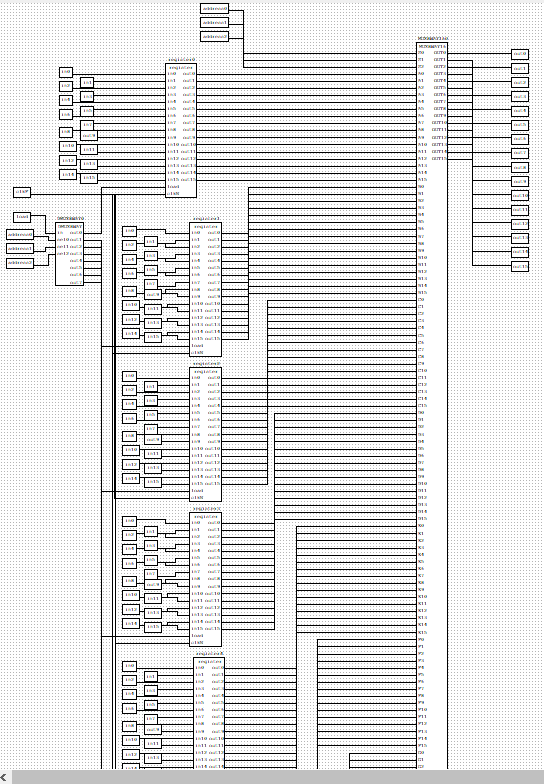

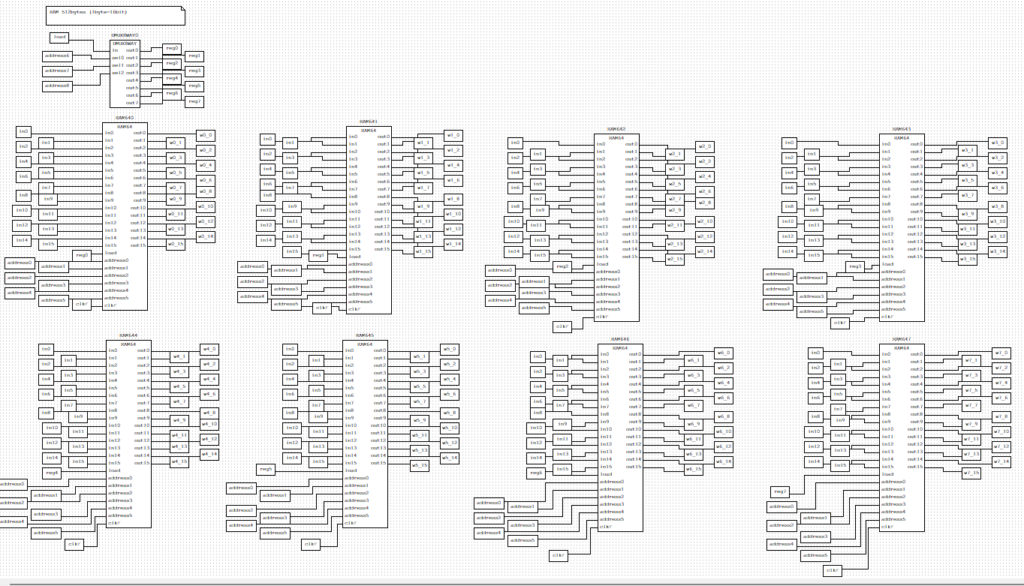

RAM8 -16ビットレジスタ8つ、アドレス付き

やばい、なんかたのしくなってきた・・・

動作確認

アドレスごとにデータの保持を確認

簡易クロック出力

OpenPLC ver4 (beta)現る

RAM64あたりで、そろそろ限界っぽい挙動(エディターが落ちる)がでてきたので 本家HPをみてみるとVer4がでてきてました。

RAM64 -省略 変数追加が重くなってきました

そろそろシステム的に限界らしいー原因箇所は不明

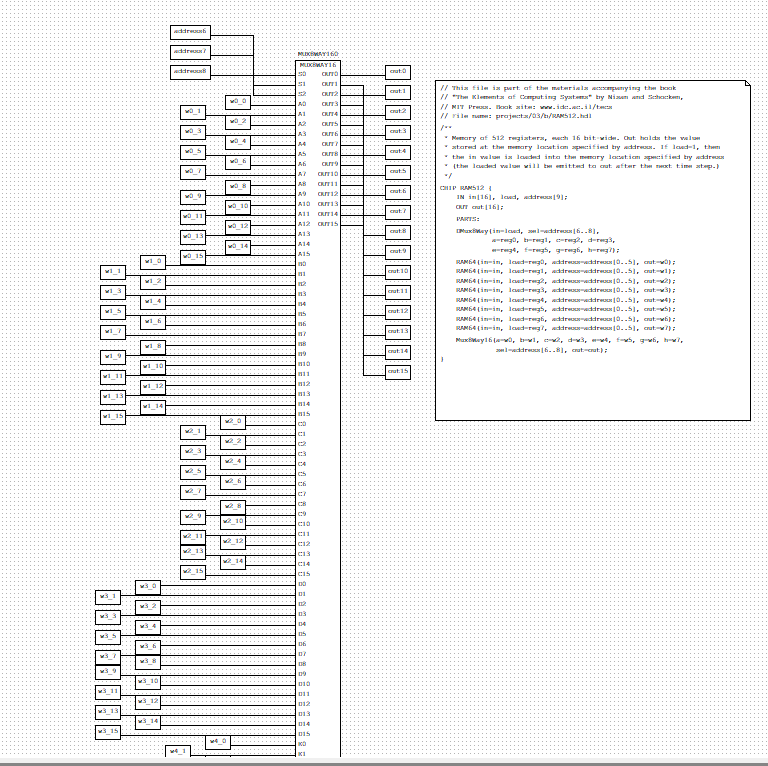

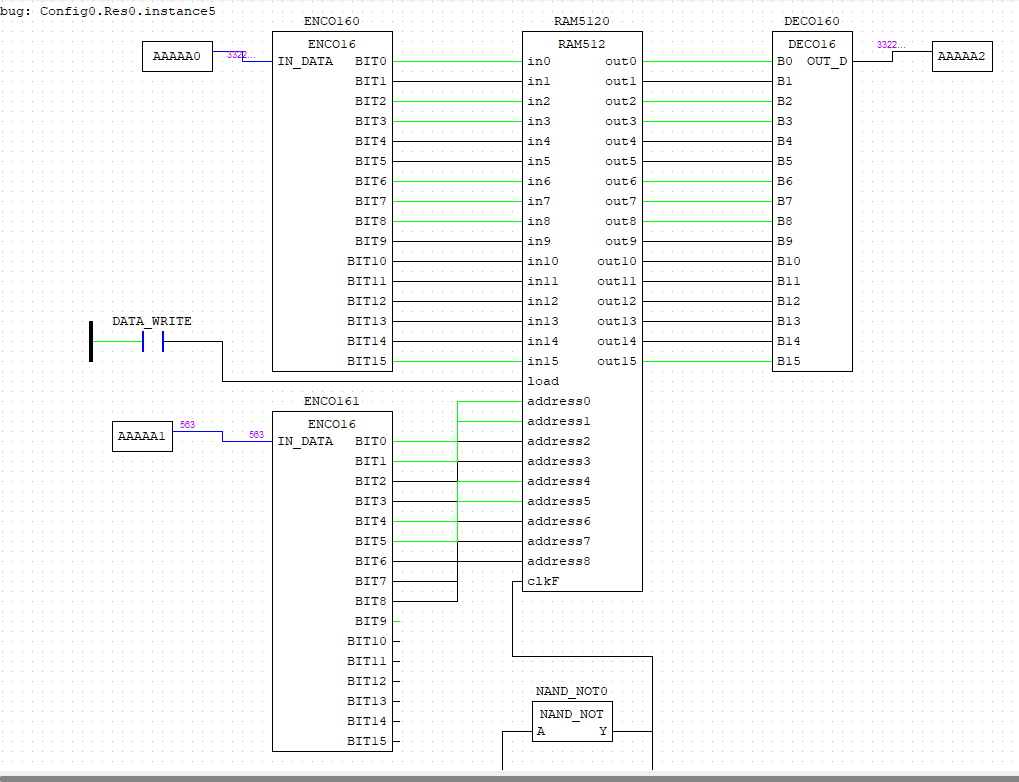

RAM512 -16ビットレジスタ512個、アドレス付き

ワイヤー接続は疲れたので変数指定に変更する

FB化で動作チェック

この時点でコンパイル時間が3分に迫るようになる

ver4で改善されるのだろうか・・・・・

どうやらOpenPLC v4は PythonからJAVA に開発環境を変えてるみたいです

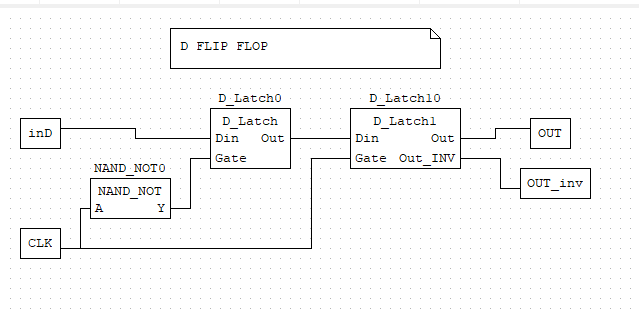

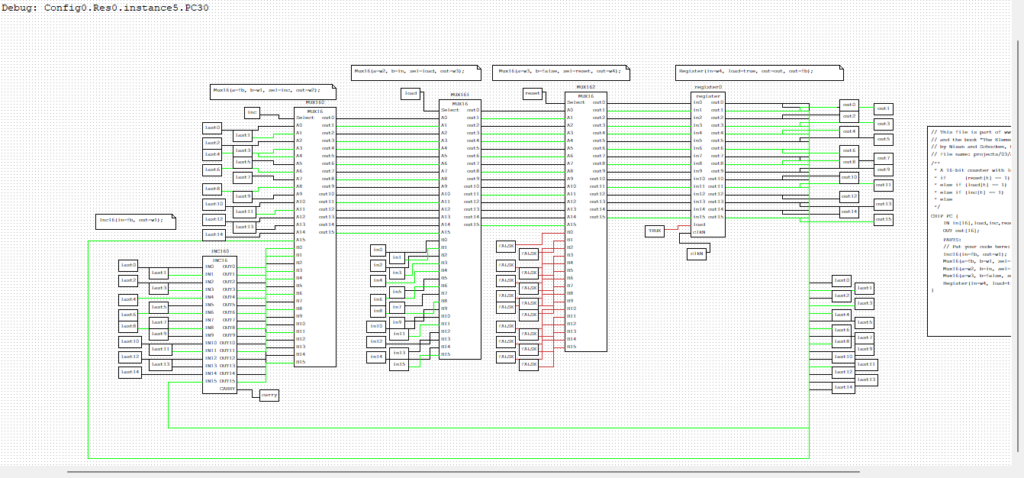

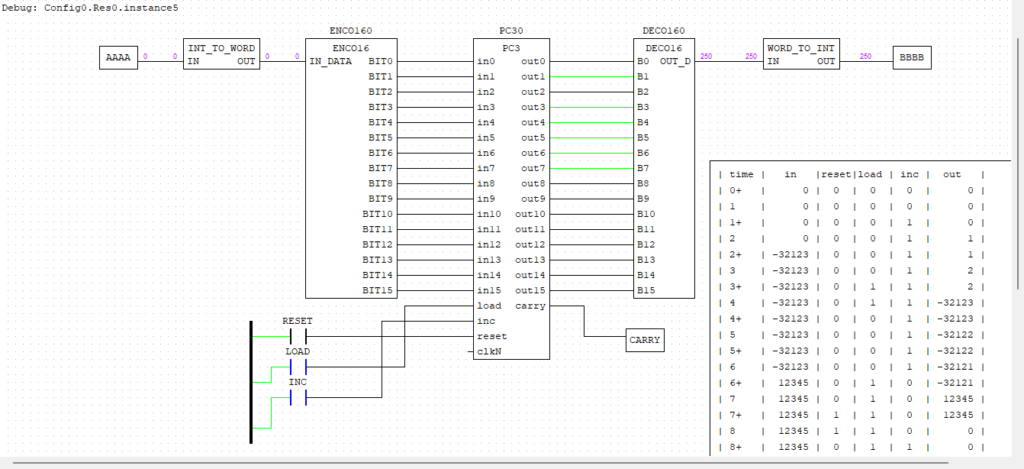

PC (PROGRAM COUNTER)

RAM512,RAM64 のFB削除するとなぜか軽くなったのでもう少しチャレンジ実行

PCはやり方が色々あるらしくこれが正解なのか不明

とりあえずカウントアップはしている模様

右下の動作確認表は見方がわかりません

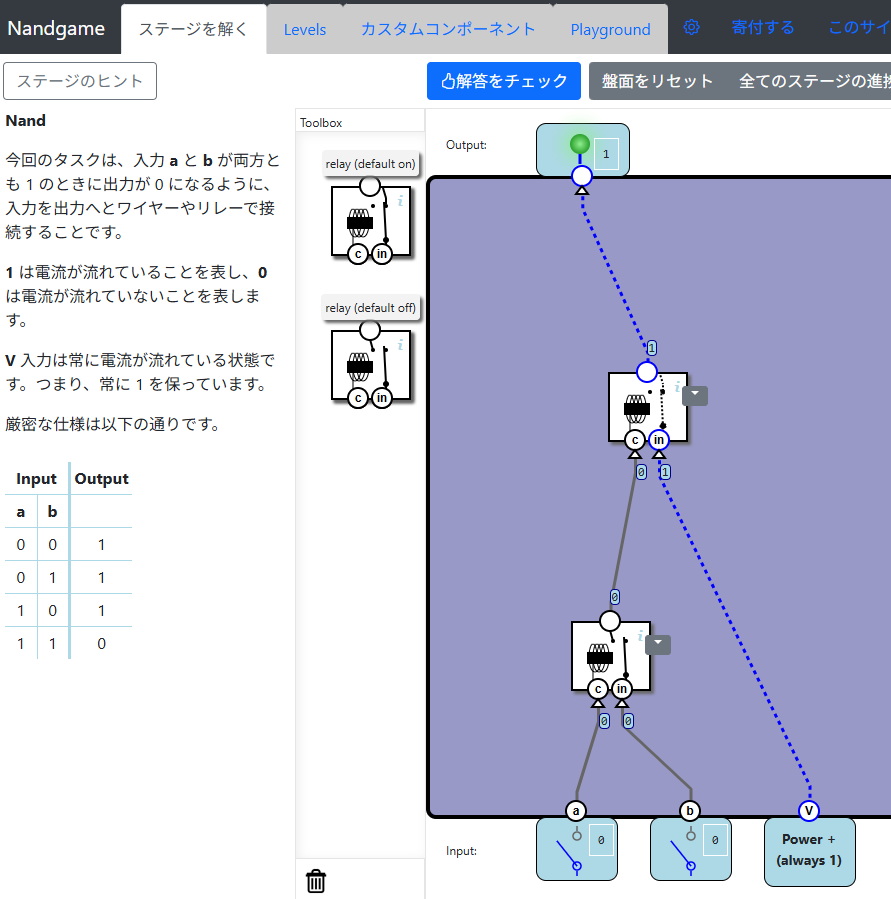

OpenPLCの限界説に、もやもやしてきたので[nandgame]をやってみた

最初の一歩:リレーが現れる!

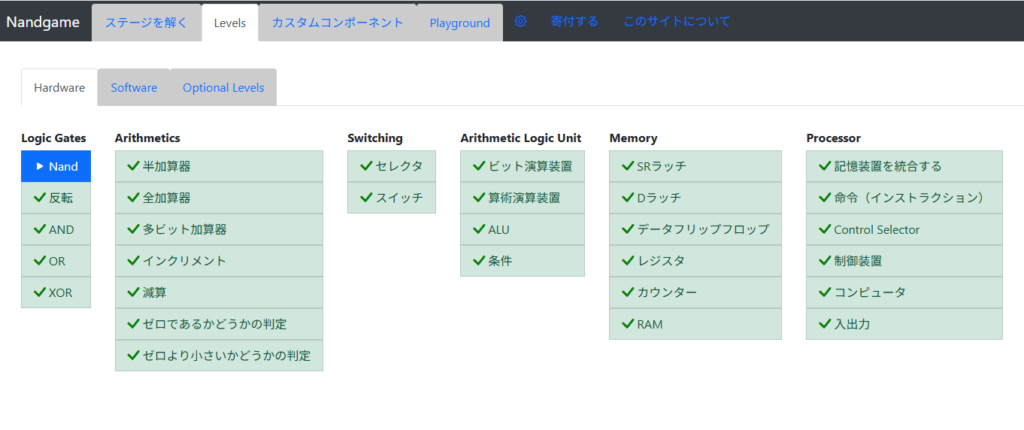

ぶっちゃけほぼカンニングで制覇【ハード部】

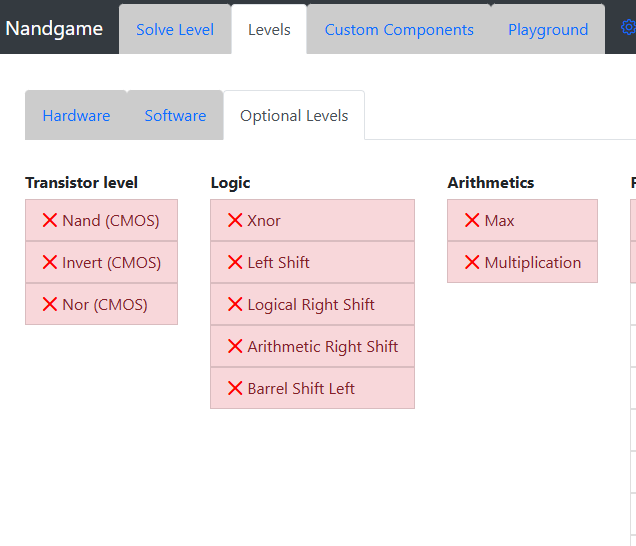

CMOS版はオプションレベルで現れるようです

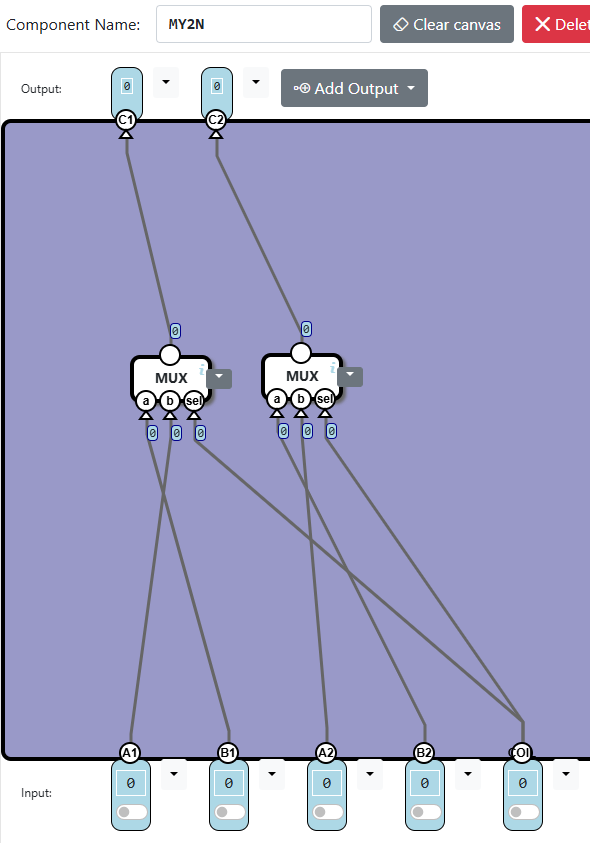

ちなみに MUX を2つでC接点2つのリレー MY2N(オムロン)ができてしまう

MUX8WAY16 [HDL をST 化するとこうなる] EDITOR:SX-EXPERT:Fuji-electric

繰り返し入力はつらいです

(*--------------------------------------------------------------------

CHIP Mux8Way16 {

IN a[16], b[16], c[16], d[16]

e[16], f[16], g[16], h[16],

sel[3];

OUT out[16];

PARTS:

Mux4Way16(a=a, b=b, c=c, d=d, sel=sel[0..1], out=muxAD);

Mux4Way16(a=e, b=f, c=g, d=h, sel=sel[0..1], out=muxEH);

Mux16(a=muxAD, b=muxEH, sel=sel[2], out=out);

}

---------------------------------------------------------------------*)

MUX4WAY16_1(

a00:=a00,a01:=a01,a02:=a02,a03:=a03,a04:=a04,a05:=a05,a06:=a06,a07:=a07,

a08:=a08,a09:=a09,a10:=a10,a11:=a11,a12:=a12,a13:=a13,a14:=a14,a15:=a15,

b00:=b00,b01:=b01,b02:=b02,b03:=b03,b04:=b04,b05:=b05,b06:=b06,b07:=b07,

b08:=b08,b09:=b09,b10:=b10,b11:=b11,b12:=b12,b13:=b13,b14:=b14,b15:=b15,

c00:=c00,c01:=c01,c02:=c02,c03:=c03,c04:=c04,c05:=c05,c06:=c06,c07:=c07,

c08:=c08,c09:=c09,c10:=c10,c11:=c11,c12:=c12,c13:=c13,c14:=c14,c15:=c15,

d00:=d00,d01:=d01,d02:=d02,d03:=d03,d04:=d04,d05:=d05,d06:=d06,d07:=d07,

d08:=d08,d09:=d09,d10:=d10,d11:=d11,d12:=d12,d13:=d13,d14:=d14,d15:=d15,

sel0:=sel0,sel1:=sel1

);

ad00:=MUX4WAY16_1.out00;

ad01:=MUX4WAY16_1.out01;

ad02:=MUX4WAY16_1.out02;

ad03:=MUX4WAY16_1.out03;

ad04:=MUX4WAY16_1.out04;

ad05:=MUX4WAY16_1.out05;

ad06:=MUX4WAY16_1.out06;

ad07:=MUX4WAY16_1.out07;

ad08:=MUX4WAY16_1.out08;

ad09:=MUX4WAY16_1.out09;

ad10:=MUX4WAY16_1.out10;

ad11:=MUX4WAY16_1.out11;

ad12:=MUX4WAY16_1.out12;

ad13:=MUX4WAY16_1.out13;

ad14:=MUX4WAY16_1.out14;

ad15:=MUX4WAY16_1.out15;

MUX4WAY16_2(

a00:=e00,a01:=e01,a02:=e02,a03:=e03,a04:=e04,a05:=e05,a06:=e06,a07:=e07,

a08:=e08,a09:=e09,a10:=e10,a11:=e11,a12:=e12,a13:=e13,a14:=e14,a15:=e15,

b00:=f00,b01:=f01,b02:=f02,b03:=f03,b04:=f04,b05:=f05,b06:=f06,b07:=f07,

b08:=f08,b09:=f09,b10:=f10,b11:=f11,b12:=f12,b13:=f13,b14:=f14,b15:=f15,

c00:=g00,c01:=g01,c02:=g02,c03:=g03,c04:=g04,c05:=g05,c06:=g06,c07:=g07,

c08:=g08,c09:=g09,c10:=g10,c11:=g11,c12:=g12,c13:=g13,c14:=g14,c15:=g15,

d00:=h00,d01:=h01,d02:=h02,d03:=h03,d04:=h04,d05:=h05,d06:=h06,d07:=h07,

d08:=h08,d09:=h09,d10:=h10,d11:=h11,d12:=h12,d13:=h13,d14:=h14,d15:=h15,

sel0:=sel0,sel1:=sel1

);

eh00:=MUX4WAY16_2.out00;

eh01:=MUX4WAY16_2.out01;

eh02:=MUX4WAY16_2.out02;

eh03:=MUX4WAY16_2.out03;

eh04:=MUX4WAY16_2.out04;

eh05:=MUX4WAY16_2.out05;

eh06:=MUX4WAY16_2.out06;

eh07:=MUX4WAY16_2.out07;

eh08:=MUX4WAY16_2.out08;

eh09:=MUX4WAY16_2.out09;

eh10:=MUX4WAY16_2.out10;

eh11:=MUX4WAY16_2.out11;

eh12:=MUX4WAY16_2.out12;

eh13:=MUX4WAY16_2.out13;

eh14:=MUX4WAY16_2.out14;

eh15:=MUX4WAY16_2.out15;

MUX16_1(

a00:=ad00,a01:=ad01,a02:=ad02,a03:=ad03,a04:=ad04,a05:=ad05,a06:=ad06,a07:=ad07,

a08:=ad08,a09:=ad09,a10:=ad10,a11:=ad11,a12:=ad12,a13:=ad13,a14:=ad14,a15:=ad15,

b00:=eh00,b01:=eh01,b02:=eh02,b03:=eh03,b04:=eh04,b05:=eh05,b06:=eh06,b07:=eh07,

b08:=eh08,b09:=eh09,b10:=eh10,b11:=eh11,b12:=eh12,b13:=eh13,b14:=eh14,b15:=eh15,

sel:=sel2 );

out00:=MUX16_1.out00;

out01:=MUX16_1.out01;

out02:=MUX16_1.out02;

out03:=MUX16_1.out03;

out04:=MUX16_1.out04;

out05:=MUX16_1.out05;

out06:=MUX16_1.out06;

out07:=MUX16_1.out07;

out08:=MUX16_1.out08;

out09:=MUX16_1.out09;

out10:=MUX16_1.out10;

out11:=MUX16_1.out11;

out12:=MUX16_1.out12;

out13:=MUX16_1.out13;

out14:=MUX16_1.out14;

out15:=MUX16_1.out15;

コメント