とりあえず開発環境を準備する

一般人からは同じに見える制御業界従事者ですが、かなり特殊なPLC文化圏です。

ラダー文化圏にも飽きてきたのでFPGAで気分転換を致しましょう。

世間はシステム設計ができれば

プログラマーは、用無しの時代がやってきました。

Copilotに相談した結果以下のようになりました

1.現状トレンドは【SystemVerilog】らしい

2.エッジAI,工場寄りの単独制御向けは【AMD】らしい

3.AMDの開発環境にワンパッケージ無償版があるっぽい!

4.【個人的イメージ】ネット上の情報割合はインテルがなんか多そう!…..えっ?

5.ニッチよりで決定w

環境の決定!

AMD開発環境 Windows11

Vivado 2025.1

インストールしてみる

ダウンロード容量:ばかでかいw

1回目:なぜか失敗

2回目:イメージごとダウンロードしたものでインストールで成功

やれやれ・・丸1日かかったよ・・・・・・

新規プロジェクトを幾つか作成してシュミレーションしてみる

プロジェクト作成後にVSCで編集::::vivadoのテキストエディタは文字を大きく出来ないようだ

コードはCopilotに出してもらう 魔法の呪文は

「vivadoで使える systemverilogの nand回路を作ってちょうだい」

モジュールファイルをソースに登録

module nand_gate (

input logic a,

input logic b,

output logic y

);

assign y = ~(a & b);

endmodule

テスト用ファイルをシミュレーションに登録

module tb_nand_gate;

logic a, b, y;

nand_gate uut (

.a(a),

.b(b),

.y(y)

);

initial begin

$monitor("a=%b b=%b y=%b", a, b, y);

a = 0; b = 0; #10;

a = 0; b = 1; #10;

a = 1; b = 0; #10;

a = 1; b = 1; #10;

$finish;

end

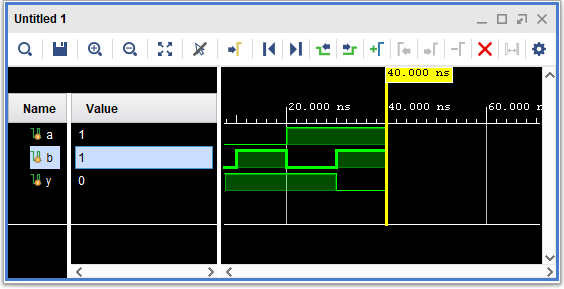

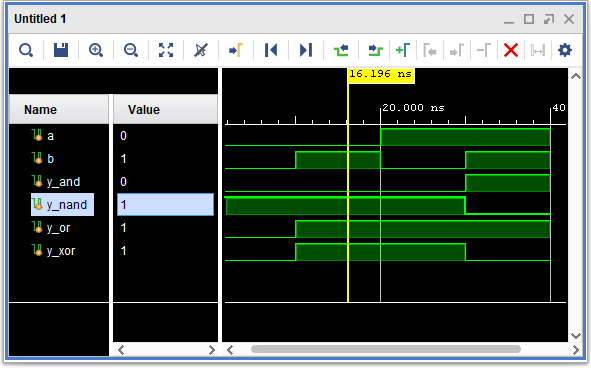

endmoduleシミュレーションしてみる

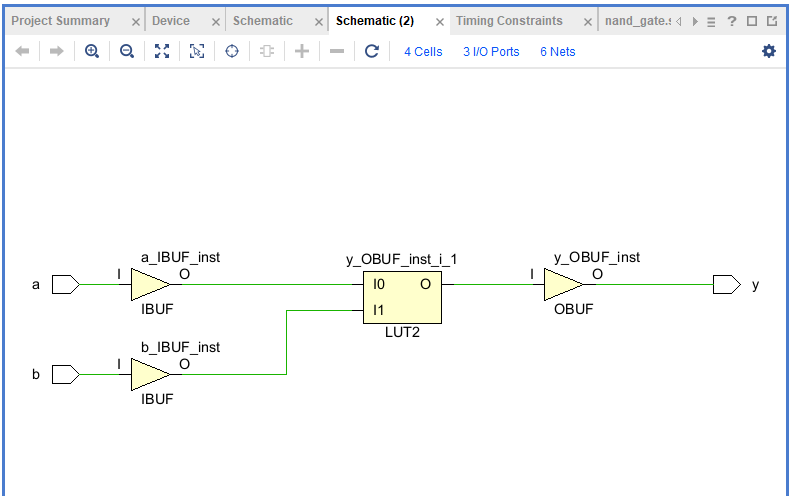

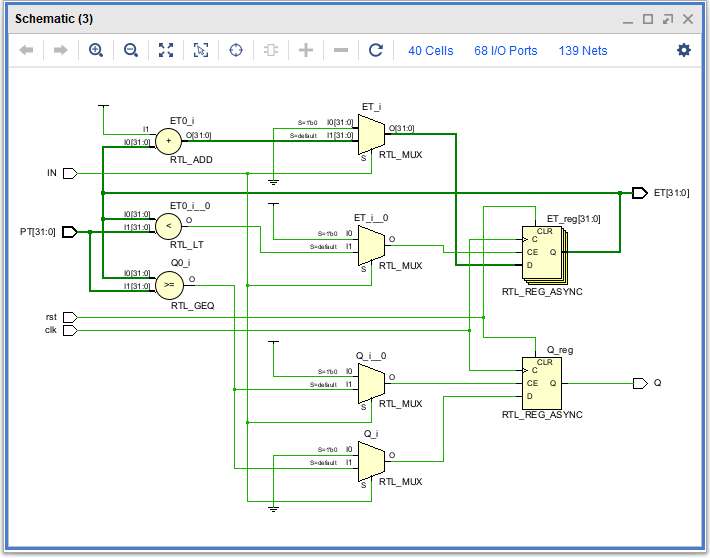

回路のイメージを出してみる

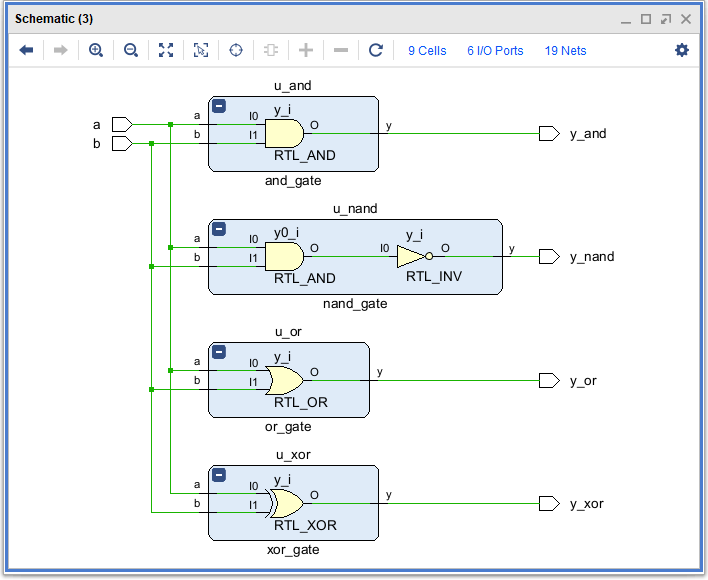

追加で and or xor まとめて出してみる - RTL Analysis –

1日目:そうだ!AIで IEC61131-3 の関数ってつくれるかな?

魔法の呪文は

「vivado systemverilog でiec61131-3のTONを作ってちょうだい。」

TON

デザインソース

module ton_timer (

input logic clk, // クロック

input logic rst, // 非同期リセット

input logic IN, // 入力信号

input logic [31:0] PT, // 設定時間(クロック数)

output logic Q, // 出力(遅延後ON)

output logic [31:0] ET // 経過時間

);

always_ff @(posedge clk or posedge rst) begin

if (rst) begin

ET <= 0;

Q <= 0;

end else begin

if (!IN) begin

ET <= 0;

Q <= 0;

end else begin

if (ET < PT)

ET <= ET + 1;

if (ET >= PT)

Q <= 1;

end

end

end

endmoduleシュミレーションソース

module tb_ton_timer;

logic clk, rst, IN;

logic [31:0] PT;

logic Q;

logic [31:0] ET;

ton_timer dut (

.clk(clk), .rst(rst), .IN(IN), .PT(PT), .Q(Q), .ET(ET)

);

// クロック生成(10ns周期)

initial clk = 0;

always #5 clk = ~clk;

initial begin

rst = 1; IN = 0; PT = 3;

#12 rst = 0;

// INをONにしてタイマ開始

#10 IN = 1;

// 10クロック分観察

repeat (10) begin

#10;

$display("Time=%0t IN=%b ET=%0d Q=%b", $time, IN, ET, Q);

end

// INをOFFにしてリセットされるか確認

IN = 0;

#20;

$finish;

end

endmodule回路のイメージ図出力

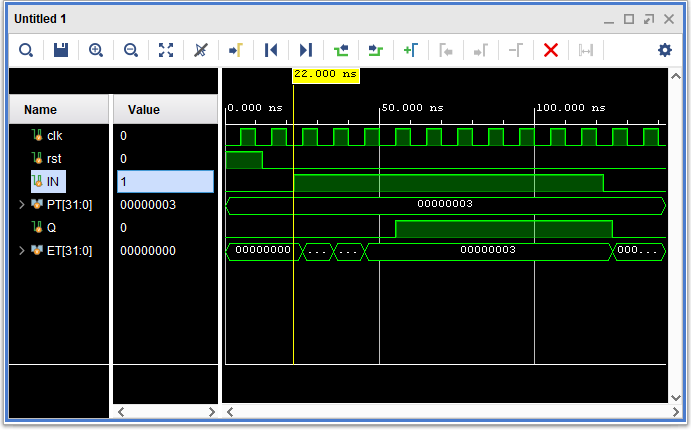

波形出力

不定期につづく

つづく

コメント