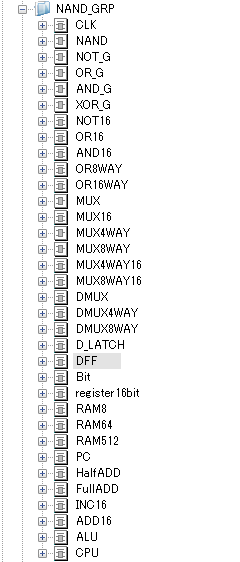

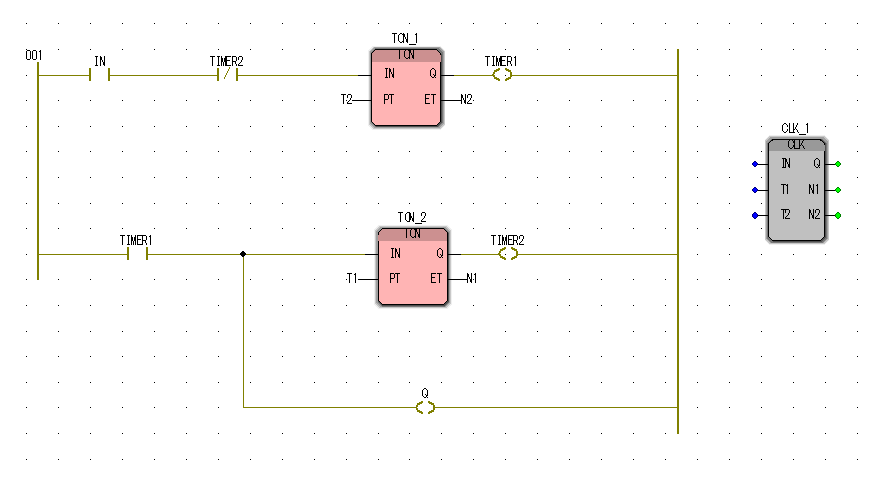

システム依存部

CLK: クロック出力 同期信号

タイマー個のフリッカ回路を利用してクロックとする

DFFはネガティブトリガー仕様なため

この出力がオフのエッジで同期する

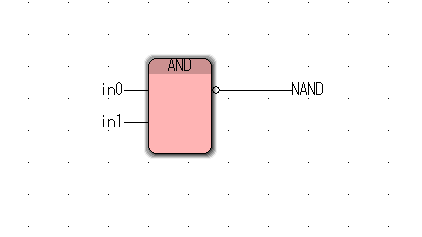

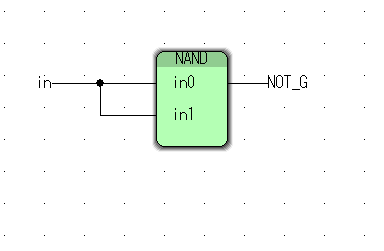

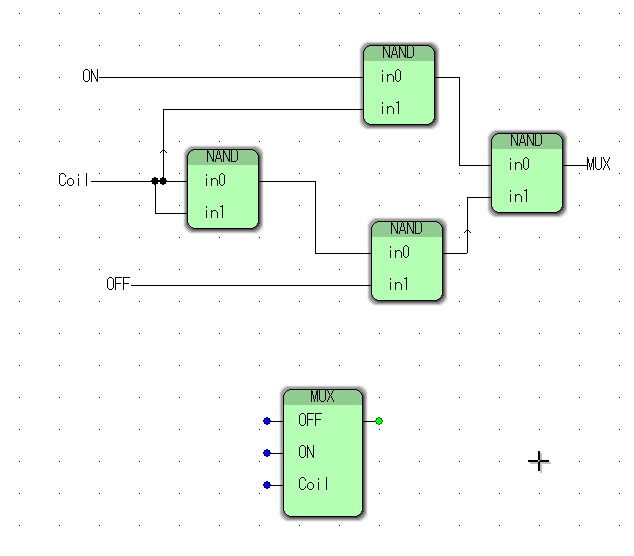

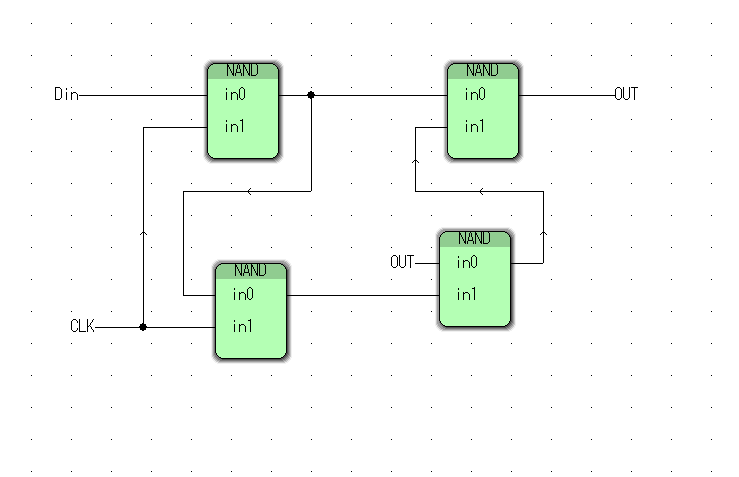

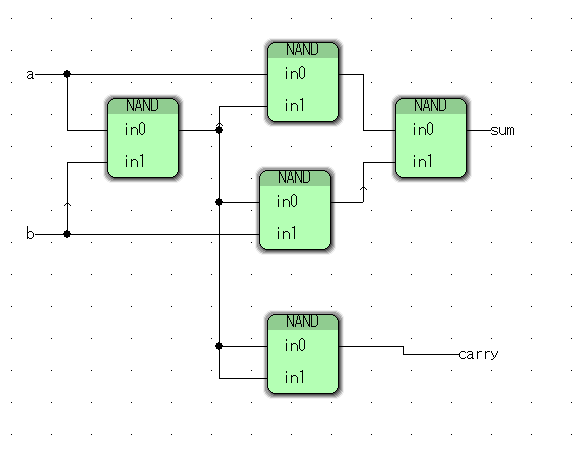

NAND

1ビット論理

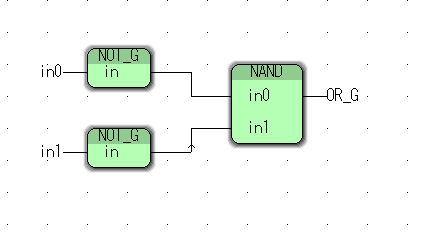

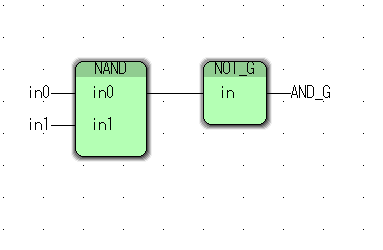

NOT

OR

AND

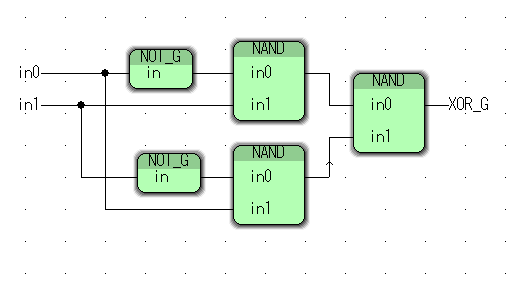

XOR

複数ビット論理

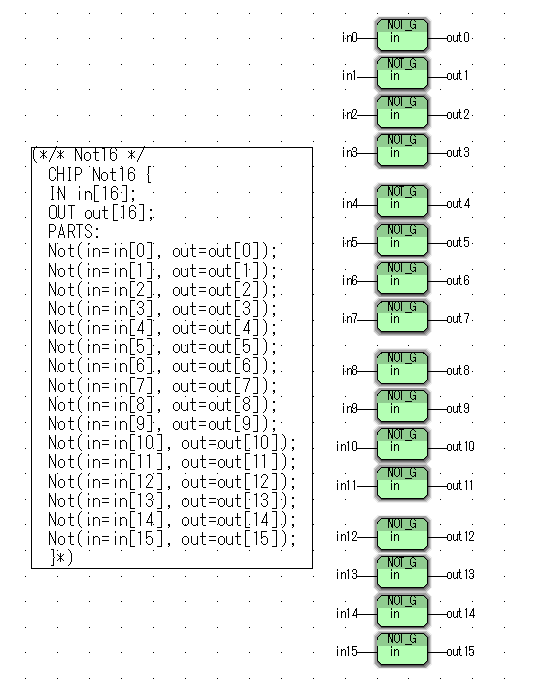

NOT16

16ビット列のNOT

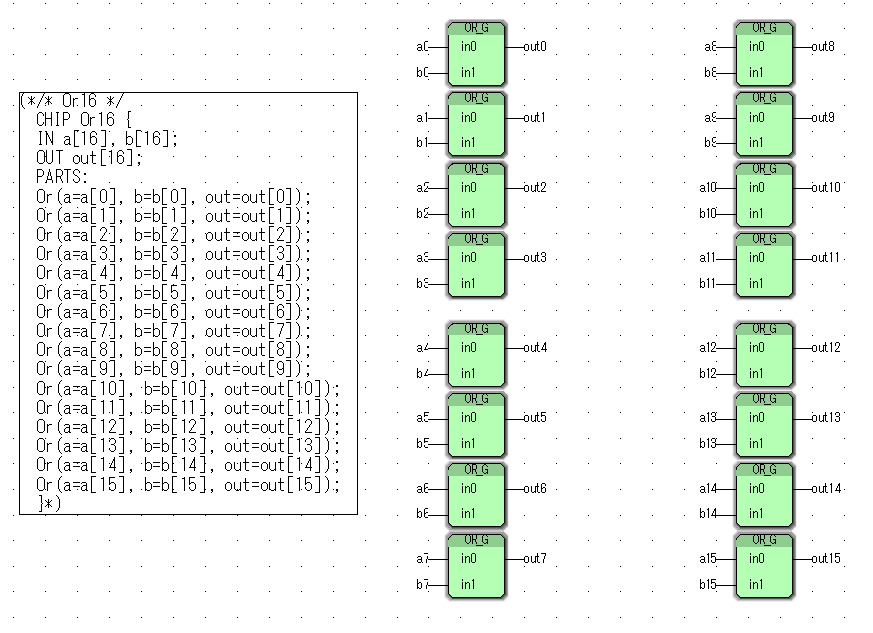

OR16

16ビット列のNOT

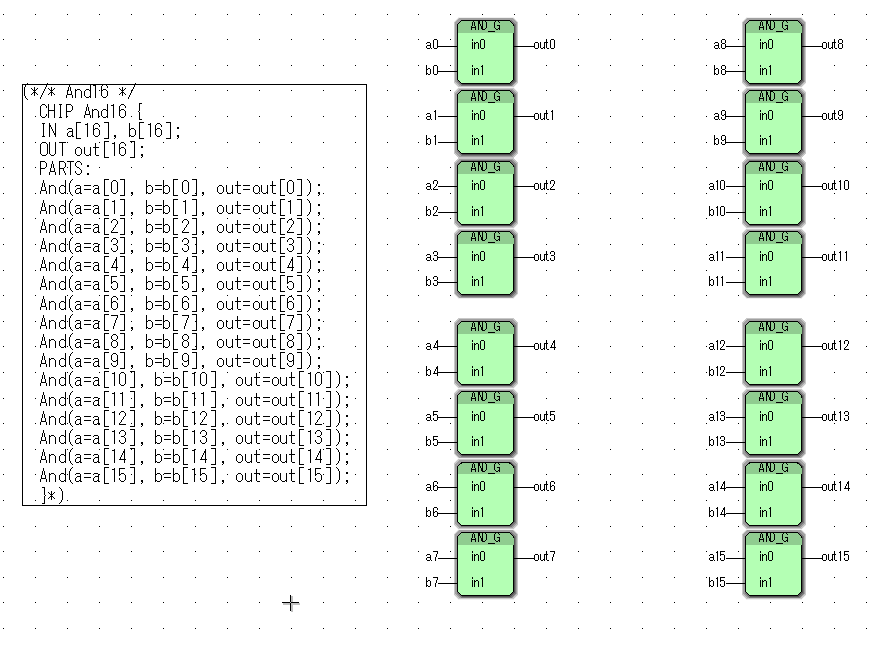

AND16

16ビット列のAND

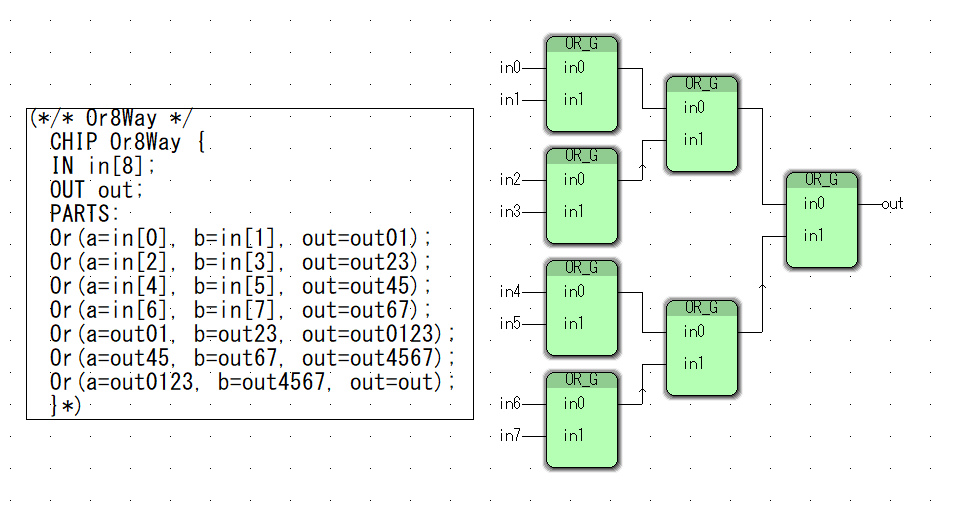

OR8WAY

8ビットのOR

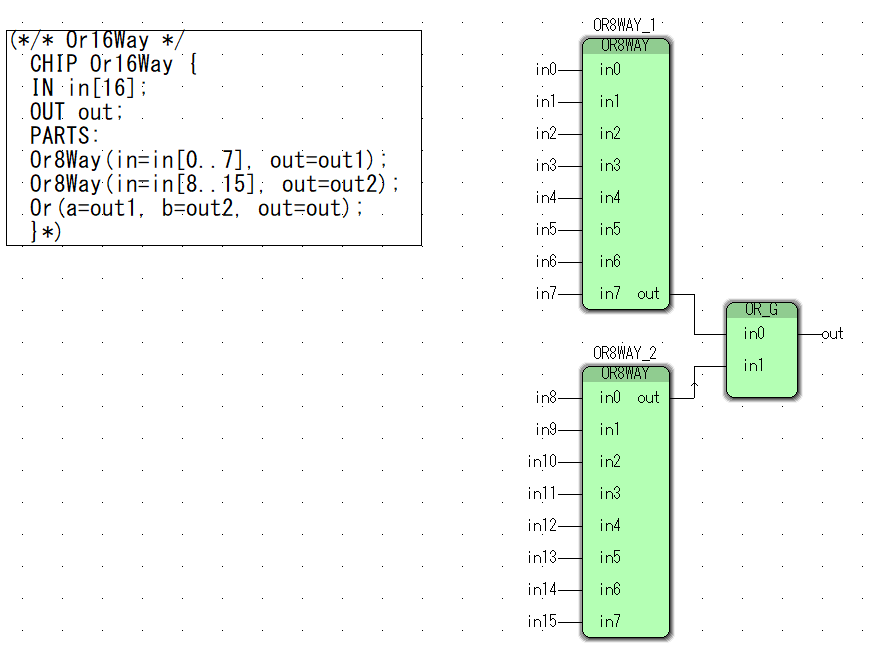

OR16WAY

16ビットのOR

選択回路

MUX

基本の選択回路

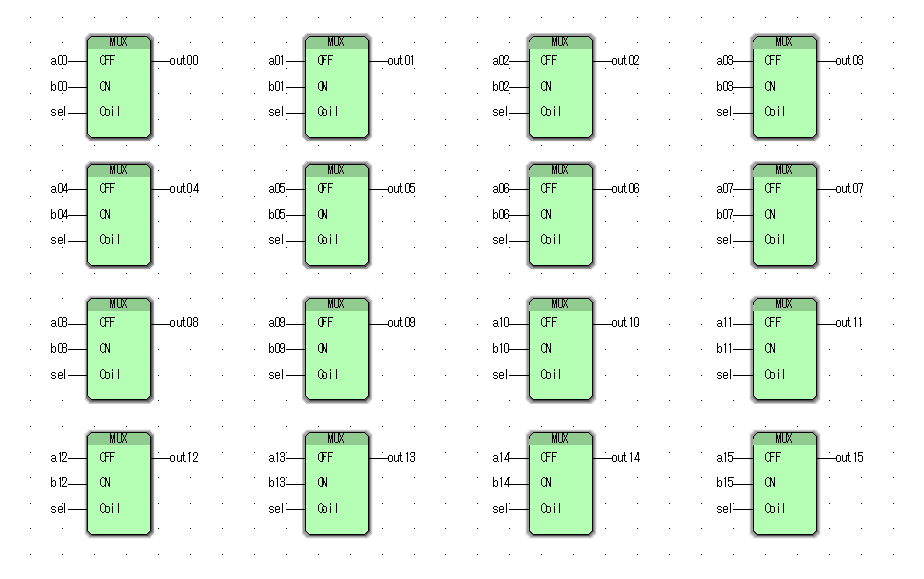

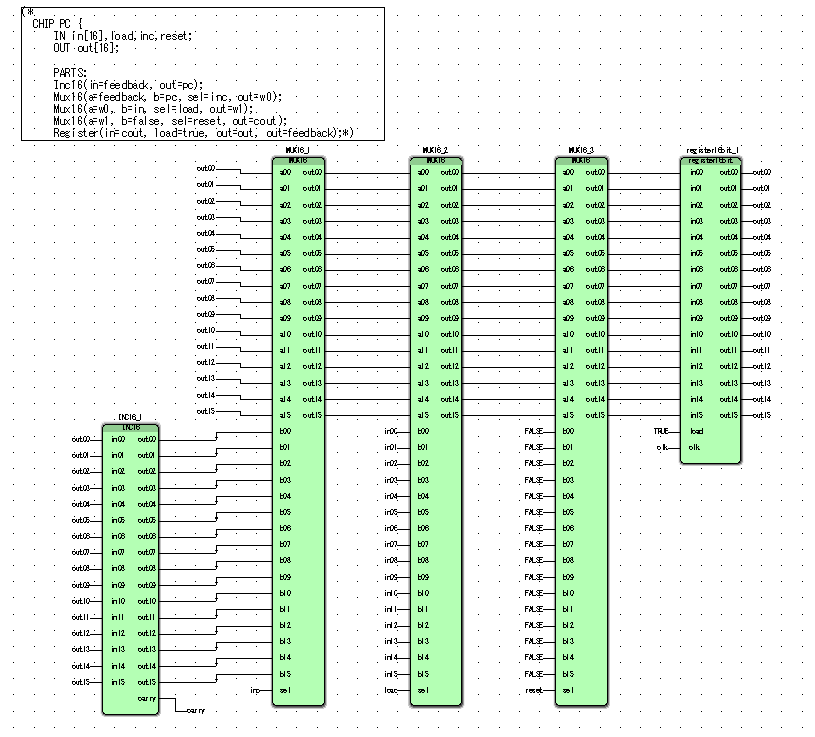

MUX16

16ビット列 選択回路

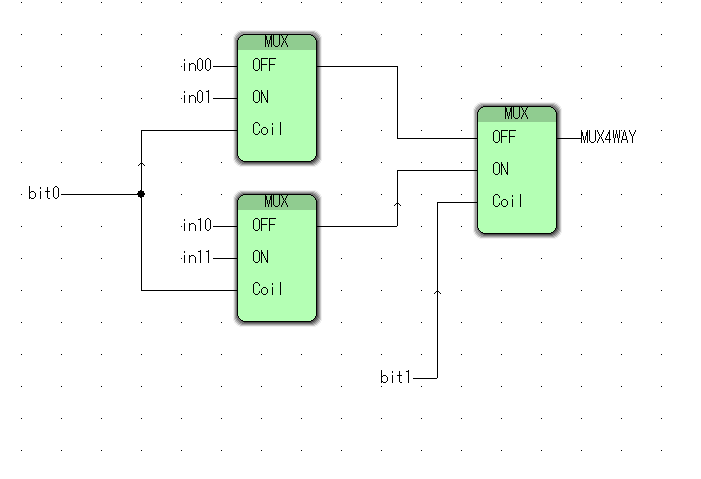

MUX4WAY

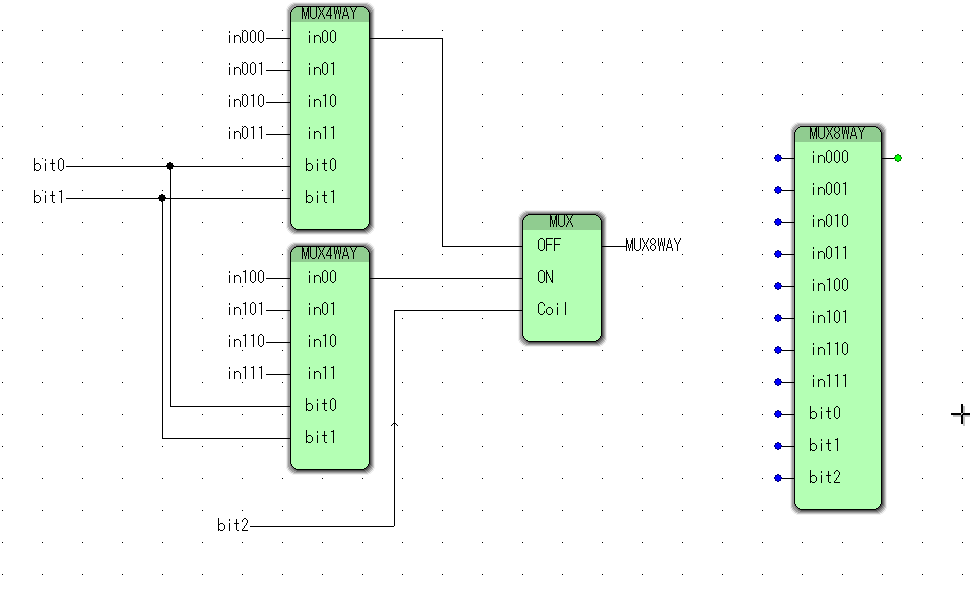

MUX8WAY

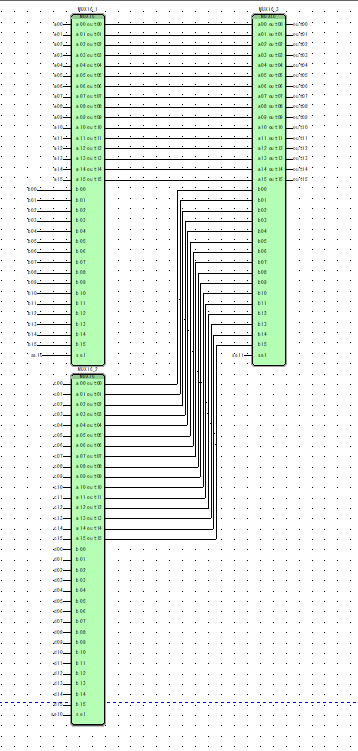

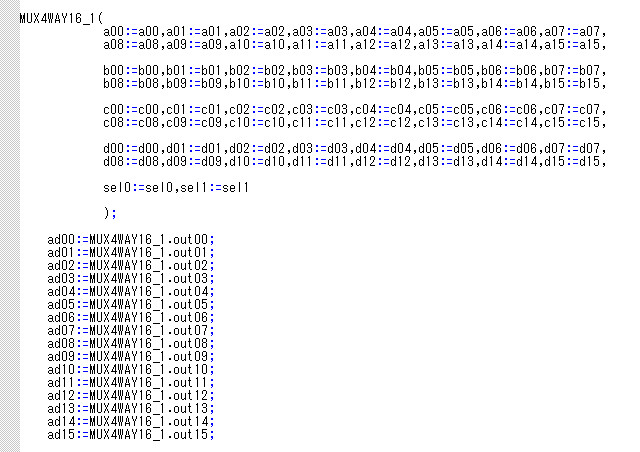

MUX4WAY16

MUX8WAY16

大きいから省略

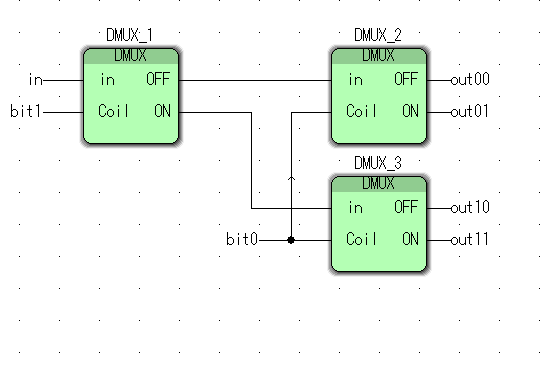

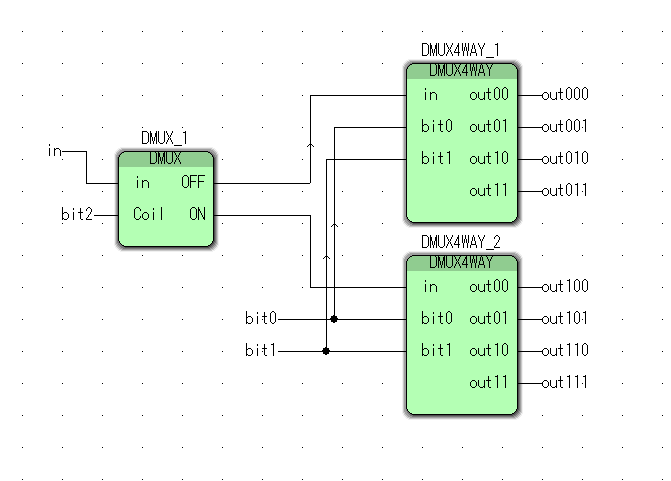

DMUX

DMUX4WAY

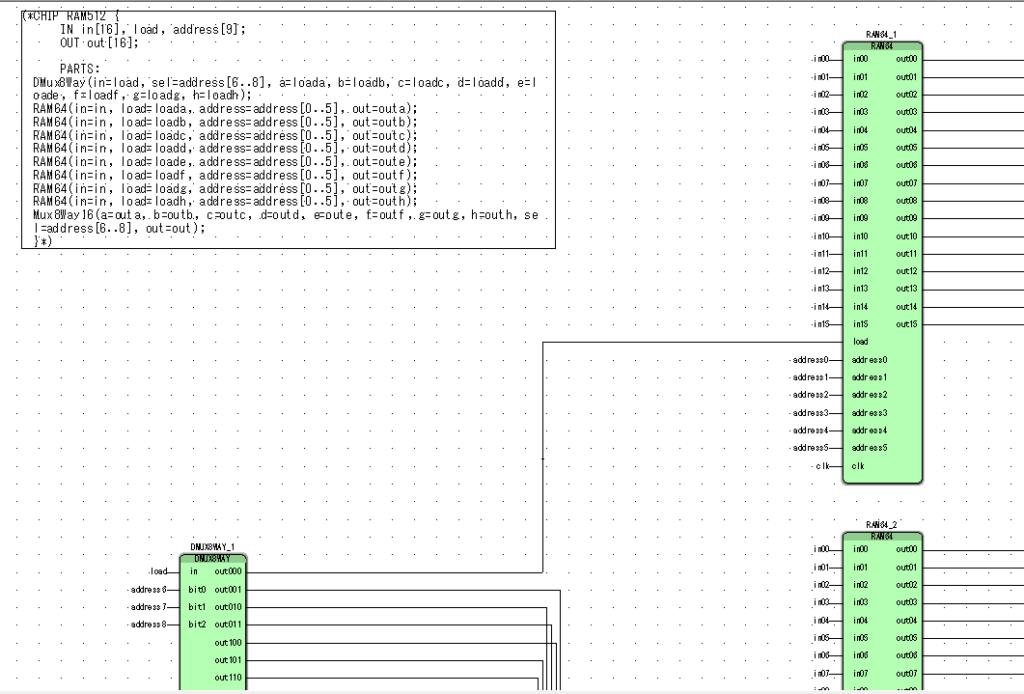

DMUX8WAY

ラッチ、メモリー

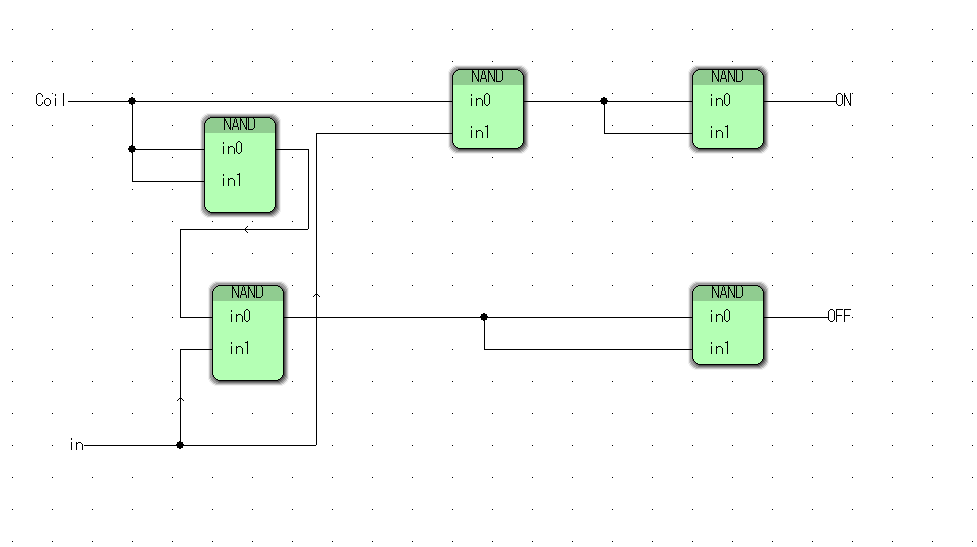

D LATCH

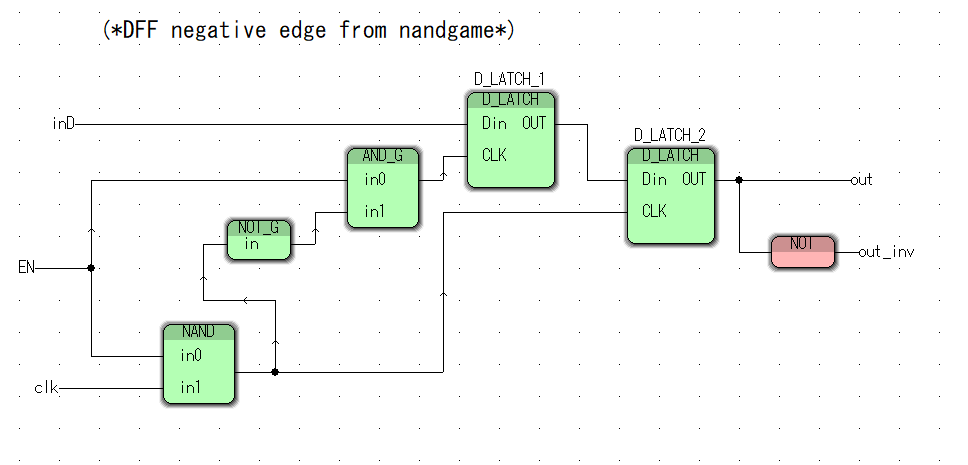

DFF

ネガティブトリガー版:オンからオフ時に同期信号を出す

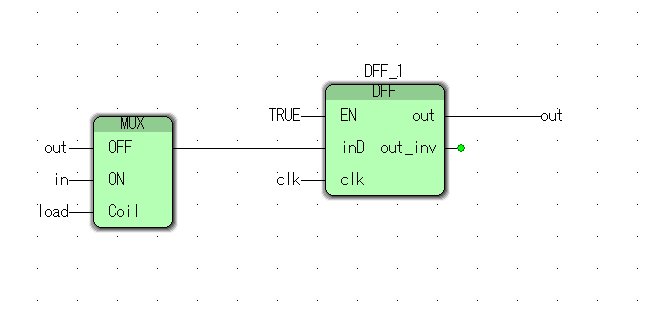

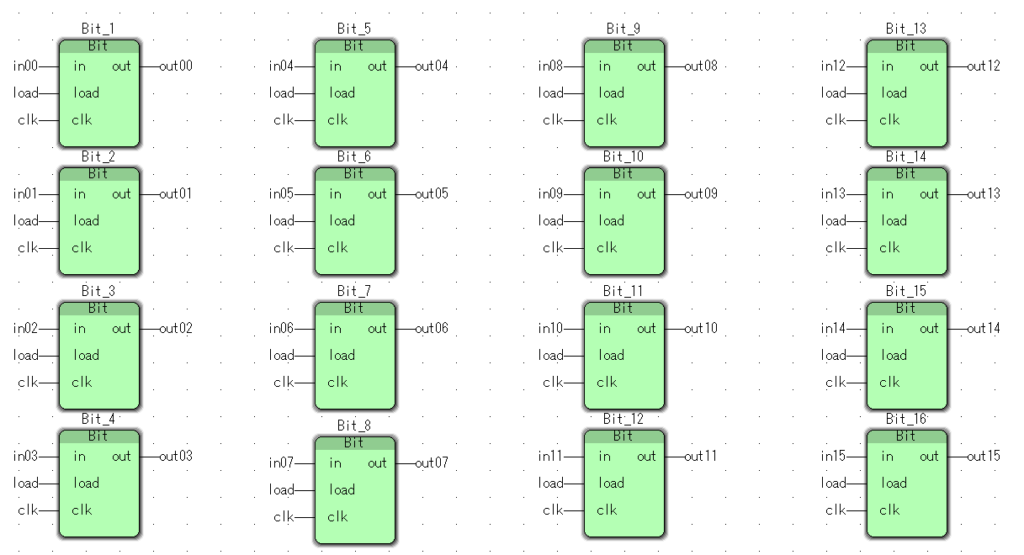

Bit

1ビットレジスタ

Register

16ビットレジスタ

RAM8

省略

RAM64

省略

RAM512

大きいから省略

RAM16k:::コーディング待機中

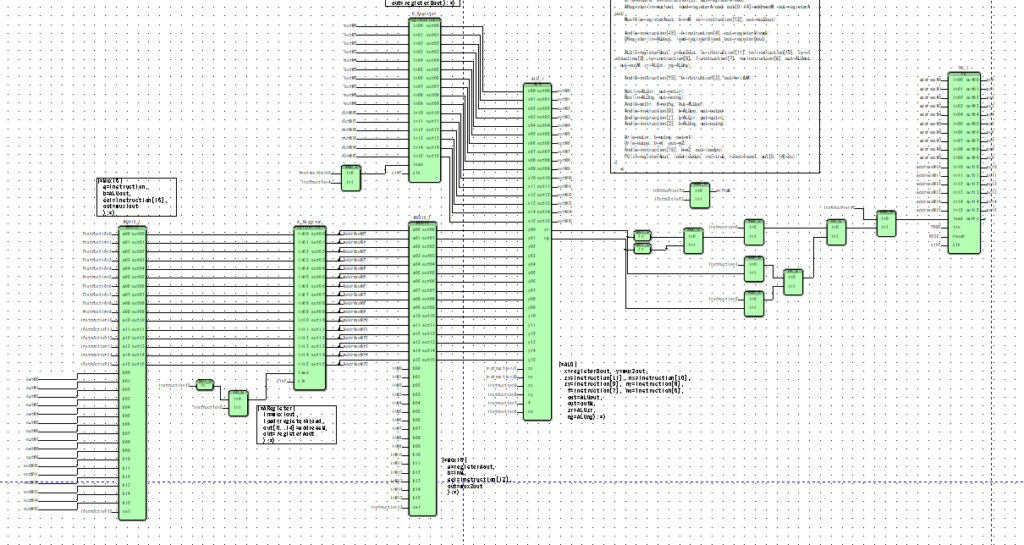

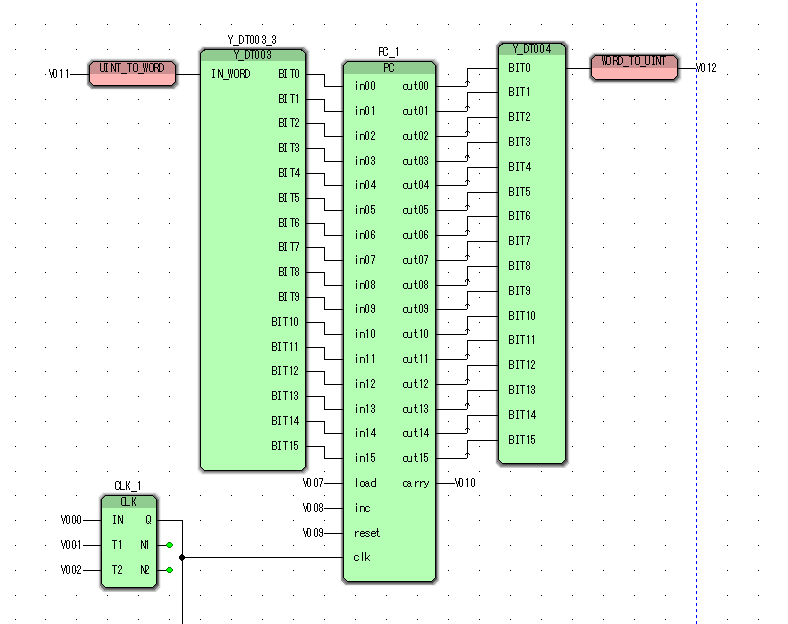

CPUに至る道

PC

プログラムカウンター

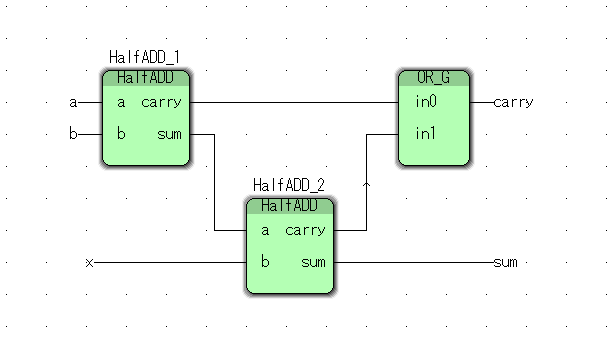

HALF ADDER

半加算器

FULL ADDER

全加算器

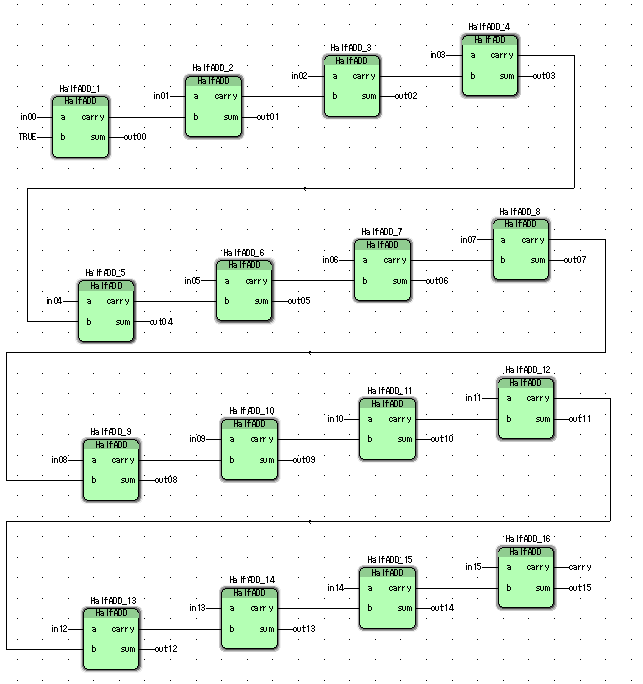

INC16

アドレス+1なやつ

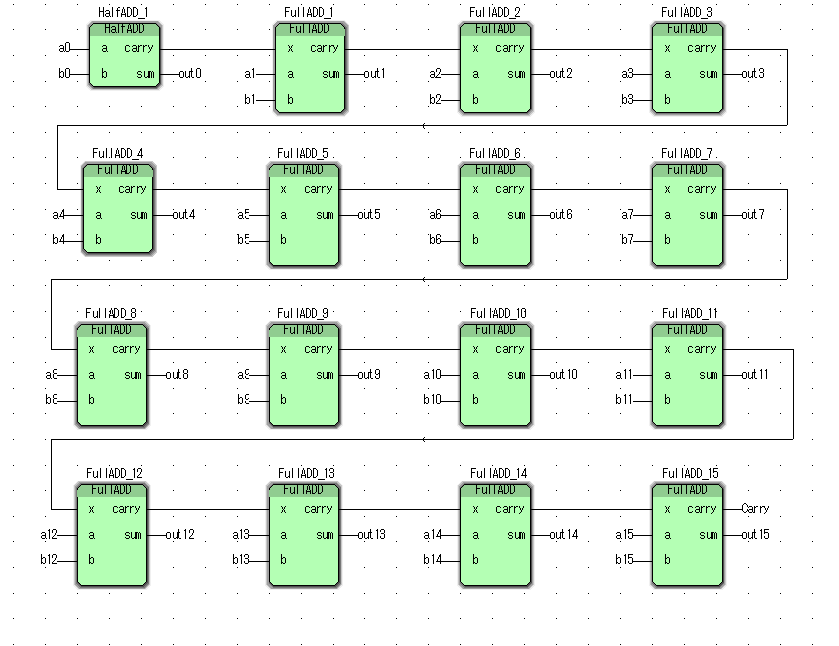

ADD16

16ビットの足し算

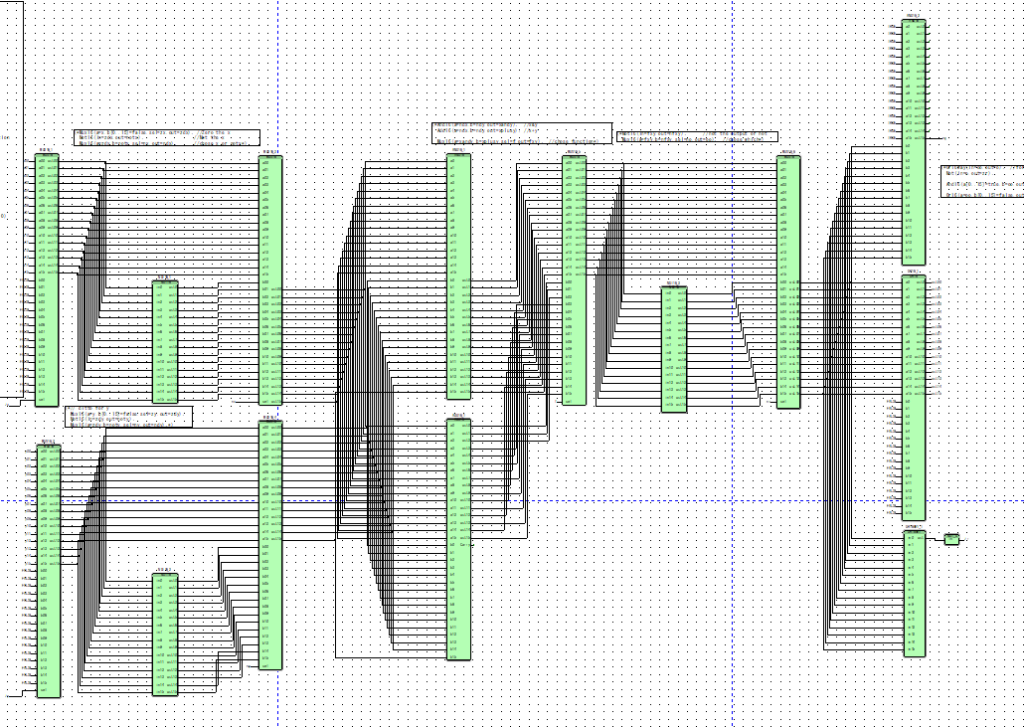

ALU

算術論理演算装置

CPU

中央演算処理装置

エディターの紹介 :これをつかってると他のがおもちゃにおもえてくるやつです

NP4H-SEDBV3 SX-Programmer Expert(D300win)

を使っています

コメント